# DR.BABASAHEB AMBEDKAR OPEN UNIVERSITY

# BCA

# **BACHELOR OF COMPUTER APPLICATION**

BCAR-203 Digital Electronics & Computer Organisation

# DIGITAL ELECTRONICS AND COMPUTER ORGANIZATION

DR. BABASAHEB AMBEDKAR OPEN UNIVERSITY AHMEDABAD

#### **Editorial Panel**

| Authors | : | Mr. Parimal Patel                          |

|---------|---|--------------------------------------------|

|         |   | I/C Director,                              |

|         |   | Kyati School of Computer Application,      |

|         |   | Ahmedabad                                  |

|         |   | Ms. Pooja Gandhi                           |

|         |   | Assistant Professor                        |

|         |   | L. J. Institute of Computer Application,   |

|         |   | Ahmedabad                                  |

| Editor  | : | Dr. Darshna Patel                          |

|         |   | Assistant Professor                        |

|         |   | Shri M. M. Patel Institute of Sciences and |

|         |   | Research, (M.Sc. IT Department),           |

|         |   | Kadi Sarva Vishwavidyalaya,                |

|         |   | Gandhinagar                                |

|         |   |                                            |

Language Editor : Dr. Jagdish Vinayakrao Anerao Associate Professor, Smt A. P. Patel Arts And, N. P. Patel Commerce College, Ahmedabad.

ISBN 978-81-949223-8-4

**Edition : 2020**

# Copyright © 2020 Knowledge Management and Research Organisation.

All rights reserved. No part of this book may be reproduced, transmitted or utilized in any form or by a means, electronic or mechanical, including photocopying, recording or by any information storage or retrieval system without written permission from us.

#### Acknowledgment

Every attempt has been made to trace the copyright holders of material reproduced in this book. Should an infringement have occurred, we apologize for the same and will be pleased to make necessary correction/amendment in future edition of this book.

#### ROLE OF SELF-INSTRUCTIONAL MATERIAL IN DISTANCE LEARNING

The need to plan effective instruction is imperative for a successful distance teaching repertoire. This is due to the fact that the instructional designer, the tutor, the author (s) and the student are often separated by distance and may never meet in person. This is an increasingly common scenario in distance education instruction. As much as possible, teaching by distance should stimulate the student's intellectual involvement and contain all the necessary learning instructional activities that are capable of guiding the student through the course objectives. Therefore, the course / self-instructional material is completely equipped with everything that the syllabus prescribes.

To ensure effective instruction, a number of instructional design ideas are used and these help students to acquire knowledge, intellectual skills, motor skills and necessary attitudinal changes. In this respect, students' assessment and course evaluation are incorporated in the text.

The nature of instructional activities used in distance education self-instructional materials depends on the domain of learning that they reinforce in the text, that is, the cognitive, psychomotor and affective. These are further interpreted in the acquisition of knowledge, intellectual skills and motor skills. Students may be encouraged to gain, apply and communicate (orally or in writing) the knowledge acquired. Intellectual-skills objectives may be met by designing instructions that make use of students' prior knowledge and experiences in the discourse as the foundation on which newly acquired knowledge is built.

The provision of exercises in the form of assignments, projects and tutorial feedback is necessary. Instructional activities that teach motor skills need to be graphically demonstrated and the correct practices provided during tutorials. Instructional activities for inculcating change in attitude and behaviour should create interest and demonstrate need and benefits gained by adopting the required change. Information on the adoption and procedures for practice of new attitudes may then be introduced.

Teaching and learning at a distance eliminate interactive communication cues, such as pauses, intonation and gestures, associated with the face-to-face method of teaching. This is particularly so with the exclusive use of print media. Instructional activities built into the instructional repertoire provide this missing interaction between the student and the teacher. Therefore, the use of instructional activities to affect better distance teaching is not optional, but mandatory.

Our team of successful writers and authors has tried to reduce this.

Divide and to bring this Self–Instructional Material as the best teaching and communication tool. Instructional activities are varied in order to assess the different facets of the domains of learning.

Distance education teaching repertoire involves extensive use of self-instructional materials, be they print or otherwise. These materials are designed to achieve certain pre-determined learning outcomes, namely goals and objectives that are contained in an instructional plan. Since the teaching process is affected over a distance, there is need to ensure that students actively participate in their learning by performing specific tasks that help them to understand the relevant concepts. Therefore, a set of exercises is built into the teaching repertoire in order to link what students and tutors do in the framework of the course outline. These could be in the form of students' assignments, a research project or a science practical exercise. Examples of instructional activities in distance education are too numerous to list. Instructional activities, when used in this context, help to motivate students, guide and measure students' performance (continuous assessment)

#### PREFACE

We have put in lots of hard work to make this book as userfriendly as possible, but we have not sacrificed quality. Experts were involved in preparing the materials. However, concepts are explained in easy language for you. We have included many tables and examples for easy understanding.

We sincerely hope this book will help you in every way you expect.

All the best for your studies from our team!

### DIGITAL ELECTRONICS AND COMPUTER ORGANIZATION

Contents

#### BLOCK 1 : NUMBER SYSTEM

#### Unit 1 NUMBER SYSTEM

Introduction, Number System, Non-positional Number Systems, Positional Number Systems, Binary Numbers, Octal Numbers, Hexadecimal Numbers, Number System Conversions

#### Unit 2 COMPUTER ARITHMETIC

Introduction, Fractional Numbers, 9's and 10's Complement, 1's and 2's Complement, Representation of Negative Numbers

#### Unit 3 CODES FOR CHARACTER REPRESENTATION

Introduction, Binary Coded Decimal, Excess 3 Code, Gray Code

#### **BLOCK 2 : BOOLEAN ALGEBRA**

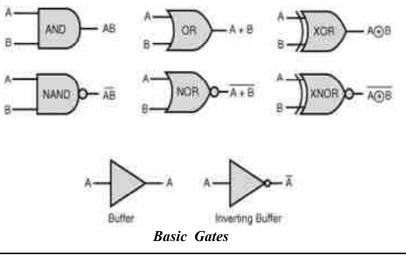

#### Unit 4 LOGIC GATES

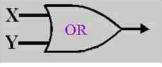

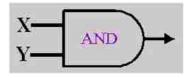

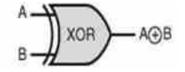

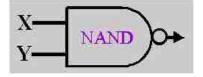

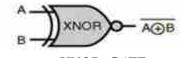

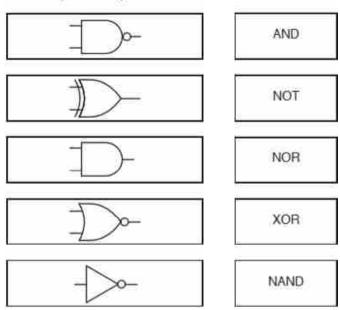

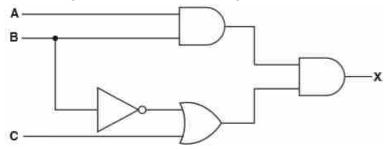

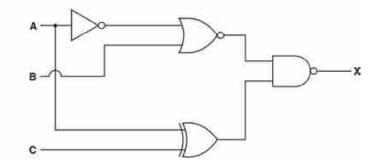

Introduction, OR GATE, AND GATE, XOR GATE, NOT GATE, NAND GATE, NOR GATE, XNOR GATE

#### Unit 5 INTRODUCTION BOOLEAN ALGEBRA

Introduction, Boolean Laws and Theorems of Boolean Algebra, Boolean Identities, Boolean Algebraic Properties

#### Unit 6 SIMPLIFICATION OF BOOLEAN ALGEBRA – I

Introduction, De Morgan's Law

#### Unit 7 SIMPLIFICATION OF BOOLEAN ALGEBRA – II

Introduction, Truth Tables, Simplification of Boolean Equation using K-Map

#### **BLOCK 3 : DIGITAL COMPONENT**

#### Unit 8 ARITHMETIC LOGIC UNIT

Introduction, Construction of ALU, Adder, Binary Half Adder, Binary Full Adder, Parallel Binary Adder, Binary Adder–Subtractor, Addition in 1's and 2's Complement System

#### Unit 9 DIGITAL COMPONENT

Introduction, Integrated Circuits, Decoders and its Expansion, Encoders, Multiplexer and its Expansion, Memory Unit

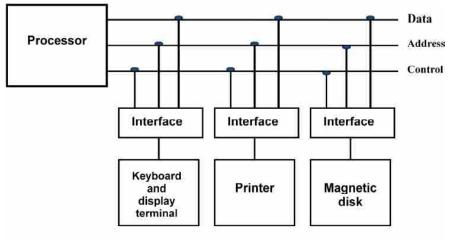

#### Unit 10 ADDRESS, DATA & CONTROL BUS

Introduction, Address, Data & Control Bus, Bus System for 4-Bit Register, Three-State Bus Buffer

#### **BLOCK 4 : INPUT/OUTPUT DEVICES AND FLIP FLOPS**

#### Unit 11 ADDRESS, DATA & CONTROL BUS

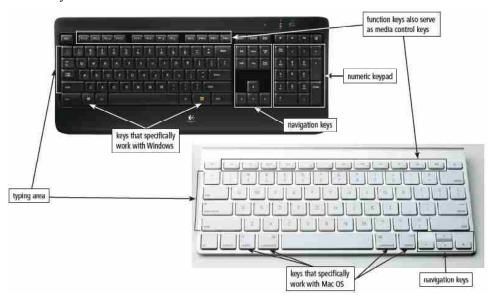

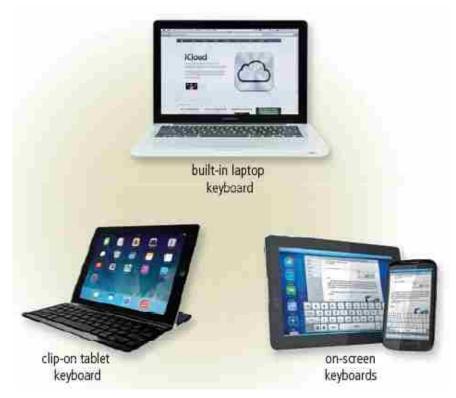

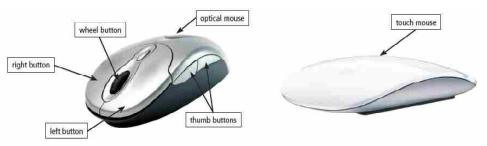

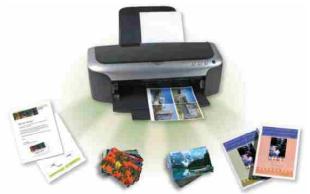

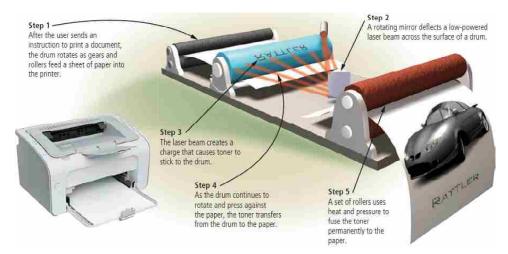

Introduction, Input/Output Devices, Key Board, Mouse, Display Unit, Printer (Types), Scanner, OCR, OMR, MICR

#### Unit 12 INPUT/OUTPUT INTERFACE and DATA TRANSFER

Introduction, Input/Output Interface, Asynchronous Data Transfer and Mode of Data Transfer, Concept of Programmed I/O, DMA

#### Unit 13 MEMORY

Introduction, Memory Hierarchy, Primary Memory, RAM and Types of RAM, ROM and Types of ROM, Secondary Memory, Magnetic Disk, Magnetic Tape, Optical Memory (CDROM), Concept of Virtual Memory, Concept of Cache and Their Need

#### Unit 14 FLIP-FLOPS

Introduction, (SR, JK, D, T) its Truth-Tables, Applications of Flip-Flops, Clocks, 3-4-bit Registers, Shift Register, Synchronous/Asynchronous Binary Counters

#### Unit 15 CPU

Introduction, Functions of CPU, Register Classification and Organization, Instruction Cycle, Instruction Formats, Addressing Modes

BAOU<br/>EducationDr. Babasaheb AmbedkarDr.Open University Ahmedabad **BCAR-203/ DCAR-203**

# **Digital Electronics and Computer Organization**

#### **BLOCK 1 : NUMBER SYSTEM**

- UNIT 1 INTRODUCTION TO NUMBER SYSTEM

- UNIT 2 COMPUTER ARITHMETIC

- UNIT 3 CODES FOR CHARACTER REPRESENTATION

## NUMBER SYSTEM

#### **Block Introduction :**

The number system that is used in our day-to-day life is called The Decimal number system. In this system, the base is equal to 10 because there are altogether ten symbols or digits (0, 1, 2, 3, 4, 5, 6, 7, 8, 9) used in this system. In the decimal system, the successive positions to the left of the decimal point represent units, tens, hundreds, thousands, etc.

The positional number system includes only the few symbols which are called as digits and these symbols represent different values depending on the position they occupy in the number. The value of every digit in such the number system is determined by three considerations.

There are two characteristics of all number systems that are recommended by the value of the base. In all the number systems, the value of the base represents the total number of different symbols or digits accessible in the number system. The first of these choices is constantly zero. The second attribute is that the highest value of the single digit is always equal to one less than the value of the base.

Maths rules are always based on the defining limits we place on the exacting numerical quantities dealt with. When we say that 2 + 2 = 4 or 5 + 4 = 9, we imply the use of integer quantities: The same types of numbers we all learn to count in basic education. Most people believe to be self-evident rules of arithmetic – valid at all times and for all purposes – It actually depend on what we define the number to be.

#### **Block Objectives :**

#### After learning this Block, you will be able to :

- Understand The number system

- Perform number conversion addition and subtraction

- Understand Fractional number representation in computer system

- Understand Negative number representation in computer system.

#### **Block Structure :**

| Unit 1 | : | Introduction to Number System      |

|--------|---|------------------------------------|

| Unit 2 | : | Computer Arithmetic                |

| Unit 3 | : | Codes for Character Representation |

Unit **01**

# NUMBER SYSTEM

### **UNIT STRUCTURE**

- 1.0 Learning Objectives

- 1.1 Introduction

- 1.2 Number System

- 1.2.1 Non-positional Number Systems

- 1.2.2 Positional Number Systems

- **1.3 Binary Numbers**

- 1.4 Octal Numbers

- 1.5 Hexadecimal Numbers

- 1.6 Number System Conversions

- 1.7 Let Us Sum Up

- 1.8 Suggested Answer for Check Your Progress

- 1.9 Glossary

- 1.10 Assignment

- 1.11 Activities

- 1.12 Case Study

- 1.13 Further Readings

#### 1.0 Learning Objectives :

#### After learning this unit, you will be able to;

- Understand number system used in computer

- Understand conversion from one number system to another

#### 1.1 Introduction :

In the computer system, data is stored in the format that cannot be simply understood by human beings. This is the cause why input and output (I/O) interfaces are essential. Each computer stores letters, numbers and the special characters in the coded form. Before going into the details of these codes, it is essential to have the basic understanding of the number system. It also introduces some of the commonly used number systems by computer professionals and the relationship between them.

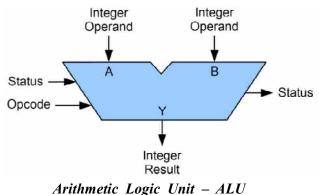

This chapter deals with the basic fundamentals of number system, computer arithmetic and binary codes. Data in the computer is stored in the series of bits which are often interpreted in blocks known as bytes [8 bits] or words. The ALU (Arithmetic and Logic Unit) performs arithmetic operations on data and the control unit needs to 'decode' instructions. Both of these jobs are performed by logic circuits.

#### 1.2 Number System :

There are two types of Number systems: non-positional and positional.

#### 1.2.1 Non – Positional Number Systems :

In very early days humans used to count fingers and ten toes there were insufficient, stones, pebbles or sticks were used to indicate values. An additive approach of counting scheme or non-positional number system uses

In this system, the symbols for 2 second, 3 for third, 4 IIII, so for 5 IIIII, I for one are used as such. Each I for 1, II for 2, III for 3, IIII for 4 etc. are used. Symbol represents the same price regardless of their position in the number and value of symbols to explore the number of demands are added. With the number system that is very difficult to perform arithmetic, positional number system was developed as the centuries passed.

#### **1.2.2 Positional Number Systems :**

In the positional number system, there are only the few symbols called digits and these symbols stand for dissimilar values depending on the position they occupy in the number. The value of each digit in such the number system is resolute by three considerations.

- 1. The digit itself

- 2. The position of The digit in The number

- 3. The base of The number system (where base is defined as The total number of digits available in The number system)

The number system that is used in our everyday life is called The Decimal number system. In this system, The base is equivalent to 10 because There are in general ten symbols or digits (0,1,2,3,4,5,6,7,8,9) used in this system. In The decimal system, the successive positions to the left of the decimal point represent units, tens, hundreds, thousands, etc.

It may also be observed that the same digit signifies different values depending upon the position it occupies in the number. For example,

In  $2586_{10}$  the digit 6 signifies 6 \*  $10^0 = 6$ In  $2568_{10}$  the digit 6 signifies 6 \*  $10^1 = 60$ In  $2658_{10}$  the digit 6 signifies 6 \*  $10^2 = 600$ In  $6258_{10}$  the digit 6 signifies 6 \*  $10^3 = 6000$

Thus, using existing digits and arranging them in the variety of positions can represent any number. The principles that relate to the decimal system relate in any additional positional number system.

The price suggested by the number of systems that all have two properties. In all systems, the base number of the price offered in the system represents the total number of different symbols or marks. The first of these options is always zero.

#### Decimal Number System :

The conventional number system used currently is the decimal number system. The decimal number system has the digits from 0 to 9 and the numbers have the base ten. The smallest number in this system is 0 and the largest number is 9. The decimal number fifty-eight is represented as  $(58)_{10}$

Any decimal number can be converted to another base by dividing the given decimal number by the base to be converted to.

#### □ Check Your Progress – 1 :

1. Explain 'positional' and 'non-positional' number system ?

2. Give example of Positional and Non–Positional Numbers.

#### **1.3 Binary Number System :**

The binary number system can be taken just like the decimal system excluding that the base is 2 instead of 10. There are only two digits (0 and 1) that can be used in this number system. We should note the largest single digit is 1 (one less than the base). Here again, each position in the binary number represents the power of The base (2). In this system, the rightmost position is the units  $(2^0)$  position, the second position from the right is the 2's  $(2^1)$  position and scheduled in this way the third position is the 4's  $(2^2)$  position, the fourth position is the 8's  $(2^3)$  position and so on. Thus, the decimal correspondent of the binary number 10101 (written as  $10101_2$ ) is

$(1 * 2^4) + (0 * 2^3) + (1 * 2^2) + (0 * 2^1) + (1 * 2^0)$ Or 16 + 0 + 4 + 0 + 1 Or 21

In order to be specific about which system is referred to, it is common practice to indicate the base as the subscript. Thus, the numbers are represented as:

$10101_2 = 21_{10}$

The common abbreviation bit often refers to 'binary digit'. Thus, the "bit" in computer technology means either the 0 or the1. The binary number consisting of n bits is called an n-bit number. Table 1.1 lists all the 3-bit numbers along with their decimal equivalent. Remember that there are only two digits, 0 and 1, in the binary system and hence the binary equivalent of the decimal number 2 has to be stated as 10 (read as one, zero).

Another important point to note is that with 3 bits (positions), only 8 (2<sup>3</sup>) different patterns of 0's and 1's are possible and from Table 1.1 it may be seen that the 3-bit number can have one of the 8 values in the range 0 to 7. In fact, it can be shown that any decimal number in the range 0 to  $2^{n}$ -1 can be represented in the binary form as an n-bit number.

| Table 1.1 | : 3–bit | Numbers | with | their | Decimal | Values |

|-----------|---------|---------|------|-------|---------|--------|

|-----------|---------|---------|------|-------|---------|--------|

| Binary | Decimal |

|--------|---------|

| 000    | 0       |

| 001    | 1       |

| 010    | 2       |

| 011    | 3       |

| 100    | 4       |

| 101    | 5       |

| 110    | 6       |

| 111    | 7       |

#### Check Your Progress – 2 :

1. Explain Decimal and Binary number system ?

..... .....

2. List all 4 bits binary numbers.

> \_\_\_\_\_ ..... .....

#### Octal Number System : 1.4

Octal number system, based on symbols or marks are only 8, 8. The system is thus : (does not exist in the system 8 and 9) 0, 1, 2, 3, 4, 5, 6 and 7. Here, The largest single digit 7 (base of less). Then, in each case based on the actual number (8) represents the power. So, (written as  $(2057)_8$ ) of the decimal equivalent of the octal number is 2057 :

$(2 * 8^3) + (0 * 8^2) + (5 * 8^1) + (7 * 8^0)$ 1024 + 0 + 40 + 7Or Or 1071

Therefore,  $2057_8 = 1071_{10}$

Observe that since there are only 8 digits in the octal number system, thus 3 bits  $(2^3 = 8)$  are sufficient to represent any octal number in binary.

One more example of octal number is  $(325)_8$ :

- $(3 * 8^2) + (2 * 8^1) + (5 * 8^0)$ 192 + 16 + 5Or

- Or  $(213)_{10}$

#### Number System

Therefore,  $2057_8 = 213_{10}$ Another example of octal number is 123 :  $(1 * 8^2) + (2 * 8^1) + (3 * 8^0)$ Or 64 + 16 + 3Or 83Therefore,  $123_8 = 83_{10}$ Check Your Progress - 3 : 1. Explain Octal Number System.

#### 1.5 Hexadecimal Number System :

In the hexadecimal number system, the base is 16. The base of 16 suggests choices of 16 single–character digits or symbols. The first 10 digits are the digits of the decimal system 0, 1, 2, 3, 4, 5, 6, 7, 8 and 9. The remaining six digits are represented by A, B, C, D, E and F representing the decimal values of 10, 11, 12, 13, 14 and 15 correspondingly.

In the hexadecimal number system, thus, the letters, A to F are used for digits 10 to 15 are number digits. The number that has the decimal equal value of 10; B has the value of 11 and A is the number that has decimal equal value of 10 so on. Thus, the largest single digit is F or 15 (one less than the base). Again, each position in the hexadecimal system represents the power of the base (16). Thus, the decimal equal of the hexadecimal number 1AF is 431.

$(1 * 16^2) + (A * 16^1) + (F * 16^0)$ Or (1 \* 256) + (10 \* 16) + (15 \* 1)Or 256 + 160 + 15Or 431Thus,  $1AF_{16} = 431_{10}$

Observe that since there are only 16 digits in the hexadecimal number system, 4 bits  $(2 \ 4 = 16)$  are sufficient to represent any hexadecimal number in binary.

#### □ Check Your Progress – 4 :

1. Explain Hexadecimal Number System.

#### 1.6 Number System Conversions :

Numbers expressed in decimal are much more meaningful than are values uttered in any other number system. Decimal numbers are used in daily life because of the fact that normally occurs. The value of the number, any number of systems can be identified in any other number system.

Input and the final output values are in decimal, decimal number system and other computer professionals often vice versa are required to change the number. To change the number from one to the other can be used by several methods or techniques.

Convert decimal to another base

Example – 1 :

The following three phases of the 10 base price of any other number systems are used to convert

Step 1 : Each issue of the column (positional) price (in this case the number of points, depending on the system) Locate.

Step 2 : To be successful with points in columns (Step 1) get into the column values.

Step 3 : Step 2 equivalent value in decimal is the total amount of the proposed products

2

\*0

0

1

\*1

1

$11001_2 = ?_{10}$ Solution : Step 1 : Determine column values Column Number Column Value (From right)  $2^0 = 1$ 1 2  $2^1 = 2$  $2^2 = 4$ 3. 4  $2^3 = 8$  $2^4 = 16$ 5 Step 2 : Multiply column values by corresponding column digits 16 8 4 \*1 \*1 \*0 8 16 0 Step 3 : Sum the products 16 + 8 + 0 + 0 + 1 = 25Hence,  $11001_2 = 25_{10}$ Example – 2 :  $4706_8 = ?_{10}$ Solution : Step 1 : Column Number Column Value

#### Number System

(From right) 1.  $8^0 = 1$ 2  $8^1 = 8$ 3.  $8^2 = 64$  $8^3 = 512$ 4. **Step 2 :** 512 1 64 8 \*4 \*7 \*0 \*6 2048 448 0 6 Step 3 : 2048 + 448 + 0 + 6 = 2502Hence,  $4706_8 = 2502_{10}$ Example – 3 :  $1AC_{16} = ?_{10}$ **Solution** :  $1AC_{16} = 1 * 16^2 + A * 16^1 + C * 16^0$ = 1 \* 256 + 10 \* 16 + 12 \* 1= 256 + 160 + 12 $= 428_{10}$

Converting from the Base 10 to the New Base

This method is also called as division – remainder technique. The following four steps are used to convert the number from base 10 to the new base.

**Step 1 :** Divide the decimal number can be converted to the new base price.

Step 2 : Divide the quotient of the division by the new base.

**Step 3 :** New to The base number (left) step 3 as the next issue remaining records.

Repeat steps 3 and 4, recording remainders from right to left, until the quotient becomes zero in step 3. Note the last remainder therefore obtained will be the most significant digit (MSD) of the new base number.

```

Example - 4 :

25_{10} = ?_2

Solution :

Steps 1 & 2 : 25/2 = 12 and remainder 1

Steps 3 & 4 : 12/2 = 6 and remainder 0

Steps 5 & 6 : 6/2 = 3 and remainder 0

Steps 7 & 8 : 3/2 = 1 and remainder 1

Steps 9 & 10 : 1/2 = 0 and remainder 1

```

As mentioned in Steps 2 & 4, the remainders have to be in order in the reverse order so that the first remainder becomes the Least Significant Digit (LSD) and the last remainder becomes The Most Significant Digit (MSD).

Hence  $25_{10} = (11001)2$ Example – 5 :  $42_{10} = ?_2$ Solution : Remainders Hence,  $42_{10} = 101010_2$ Example – 6 :  $952_{10} = ?_8$ Solution : Remainders

Hence,  $952_{10} = 1670_8$

#### Number System

#### Example - 7 :

$428_{10} = ?_{16}$

#### Solution :

| 16     | 428              | Remainders in hexadecimal |

|--------|------------------|---------------------------|

|        | 26               | 12 = C                    |

|        | 1                | 10 = A                    |

|        | 0                | 1 = 1                     |

| Hence, | $428_{10} = 1A6$ | C <sub>16</sub>           |

Converting from the base other than 10 to the base other than 10

The subsequent two steps are used to convert the number from the base other than 10 to the base other than 10.

Step1 : Convert the original number to the decimal number (base 10).

Step2 : Convert the decimal number so obtained to the new base.

Example - 8 : 101110<sub>2</sub> = ?<sub>8</sub> Solution : Step1 : Convert 101110<sub>2</sub> to base 10 1011102 = 1 \* 2<sup>5</sup> + 0 \* 2<sup>4</sup> + 1 \* 2<sup>3</sup> + 1 \* 2<sup>2</sup> + 1 \* 2<sup>1</sup> + 0 \* 2<sup>0</sup> = 32 + 0 + 8 + 4 + 2 + 0 = 46<sub>10</sub> Step2 : Convert 46<sub>10</sub> to base 8. 8 46 Remainders 5 - 6 6 5 - 6Hence, 46<sub>10</sub> = 56<sub>8</sub> So, 101110<sub>2</sub> = 46<sub>10</sub> = 56<sub>8</sub> Thus, 101110<sub>2</sub> = 56<sub>8</sub>

Shortcut methods for conversions

There are shortcut methods of conversion from one base to another. The octal number can be converted to hexadecimal format without being converted to decimal and then being divided by 16. Each digit of the octal number are split and represented by equivalent binary numbers of 3 bits each. And the binary number can then be grouped into 4 bits each for representing the hexadecimal number. The shortcut methods of conversion are as follows:

Binary to Octal

The subsequent steps are used in this method :

**Step 1 :** Divide the binary digits into groups of three (initial from the right).

Step 2 : Convert each group of three binary digits into one octal digit.

Since decimal digits 0 to 7 are equal to octal digits 0 to 7 so binary to decimal conversion can be used in this step.

```

Example - 9 :

101110_2 = ?_8

Solution :

Step 1 : Divide the

```

**Step 1 :** Divide the binary digits into groups of 3 starting from right (LSD)

<u>101</u> <u>110</u>

**Step 2 :** Convert each group into one digit of octal (use binary–to–decimal conversion)

```

101_{2} = 1 * 2^{2} + 0 * 2^{1} + 1 * 2^{0}

= 4 + 0 + 1

= 5<sub>8</sub>

110_{2} = 1 * 2^{2} + 1 * 2^{1} + 0 * 2^{0}

= 4 + 2 + 0

= 6<sub>8</sub>

```

Therefore,  $101110_2 = 56_8$

Octal to Binary

The subsequent steps are used in this method:

**Step 1 :** Each octal digit to convert the three –digit binary number (octal digits for the conversion can be represented as decimal)

**Step 2 :** The out coming binary groups combined in the single binary number (3 points each) are covered

Example - 10 :

$$562_8 = ?_2$$

#### Solution :

Step 1 : Convert each octal digit to 3 binary digits.

```

5_8 = 101_2

6_8 = 110_2

2_8 = 010_2

Step 2 : Combine the binary groups.

562_8 = 101110010_2

Hence, 562_8 = 101110010_2

Example - 11 :

6751_8 = ?_2

Solution :

67518 = 110111101001_2

= 110111101001_2

```

Hence,  $6751_8 = 110111101001_2$

Binary to Hexadecimal

The following steps are followed under this method :

Step 1 : (Starting from right) Divide in groups of four binary digits

**Step 2 :** Each group of four binary digits in the hexadecimal digits converted. (0–9 hexadecimal digits hexadecimal digits 0 to 9 and decimal points are equal. F. for 10 to 15 F for the decimal must be represented as hexadecimal values are equivalent to 10 to 15 decimal digits).

Example - 12 :

$11010011_2 = ?_{16}$

Solution :

Step 1 : Divide the binary digits into groups of 4.

#### <u>1101 0011</u>

Step 2 : Convert each group of 4 binary digits to 1 hexadecimal digit.

$$1101_{2} = 1 * 2^{3} + 1 * 2^{2} + 0 * 2^{1} + 1 * 2^{0}$$

= 8 + 4 + 0 + 1

= 13<sub>10</sub>

= D<sub>16</sub>

0011\_{2} = 0 \* 2^{3} + 0 \* 2^{2} + 1 \* 2^{1} + 1 \* 2^{0}

= 0 + 0 + 2 + 1

= 3<sub>16</sub>

Hence, 11010011\_{2} = D3<sub>16</sub>

Example - 13 :

$$10110101100_2 = ?_{16}$$

Solution :

$10110101100_2 = 010110101100$

(Group 4 digits from right)

$$= 5AC$$

(Convert each group to the hexadecimal digit)

Hence,  $10110101100_2 = 5AC_{16}$

Hexadecimal to Binary

The following steps are used in this method:

**Step 1 :** Convert the decimal equivalent of hexadecimal digit to 4 bit binary number.

**Step 2 :** Combine all the out coming binary groups (of 4 digits each) into single binary number.

Example – 14 :

$2AB_{16} = ?_2$

Solution :

**Step 1 :** Convert the decimal equivalent of each hexadecimal digit into 4 binary digits.

$2_{16} = 2_{10} = 0010_{2}$   $A_{16} = 10_{10} = 1010_{2}$   $B_{16} = 11_{10} = 1011_{2}$ Step 2 : Combine the binary groups  $2AB_{16} = 001010101011_{1}$ 2 the B

Hence,  $2AB_{16} = 0010101010101_{2}$ Example - 15 :  $ABC_{16} = ?_{2}$ Solution :  $ABC_{16} = 101010111100_{1}$ the B C  $= 101010111100_{2}$ Hence,  $ABC_{16} = 101010111100_{2}$

| Table | 1.2 | : | Relationship | ) between | Dec  | imal, | Hexadecimal, |

|-------|-----|---|--------------|-----------|------|-------|--------------|

|       |     | E | Binary and C | Octal Nur | nber | Syste | ems          |

|         | and Octai Num | ber Systems |       |

|---------|---------------|-------------|-------|

| Decimal | Hexa Decimal  | Binary      | Octal |

| 0       | 0             | 0           | 0     |

| 1       | 1             | 1           | 1     |

| 2       | 2             | 10          | 2     |

| 3       | 3             | 11          | 3     |

| 4       | 4             | 100         | 4     |

| 5       | 5             | 101         | 5     |

| 6       | 6             | 110         | 6     |

| 7       | 7             | 111         | 7     |

| 8       | 8             | 1000        | 10    |

| 9       | 9             | 1001        | 11    |

| 10      | А             | 1010        | 12    |

| 11      | В             | 1011        | 13    |

| 12      | С             | 1100        | 14    |

| 13      | D             | 1101        | 15    |

| 14      | Е             | 1110        | 16    |

| 15      | F             | 1111        | 17    |

Finally, the above Table 1.2 summarises the relationship between the decimal, binary, hexadecimal and octal number systems. Note that the maximum value for the single digit of octal (7) is equal to the maximum value of three digits of binary. The value range of one digit of octal duplicates the value range of three digits of binary. If octal digits are substituted for binary digits, the substitution is on the one-to-three basis.

#### Number System

Similarly, note that the maximum value of one digit in hexadecimal is equal to the maximum value of four digits in binary. Thus, the value range of one digit of hexadecimal is equivalent to the value range of four digits of binary. Therefore, hexadecimal shortcut notation is the one-to-four reduction in the space and time required for memory dump.

#### Check Your Progress - 5 :

1. Explain Number system conversion from binary to decimal, hexadecimal and octal with example.

..... ..... \_\_\_\_\_ ..... 2. The decimal equivalent of 1000 is \_\_\_\_\_ (a) 2 (b) 4 (c) 6 (d) 8 The binary number 1100 is equal to \_\_\_\_\_\_ decimal number. 3. (a) 9 (b) 10 (c) 12 (d) 0Convert in to decimal : (214)8 = ?4. (b) 141 (a) 140 (c) 142 (d) 130 The octal number equivalent of 110110 is \_\_\_\_\_ 5. (d) 55 (a) 66 (b) 88 (c) 77 The binary number 11001010 is equal to \_\_\_\_\_ hexadecimal number. 6. (a) CA (b) AB (c) 1A (d) B1 7. The Hexadecimal representation of 1110 is \_ (a) 0111 (b) E (c) 15 (d) 14 1.7 Let Us Sum Up :

Number systems are of two types-non positional and positional. In the non-positional number system, every symbol determines the same value regardless of its position in The number and to find the value of the number, one has to count the number of symbols present in The number.

Some positional number system that are used in computer design and by computer professionals are binary, octal and hexadecimal.

| 1.8 | Answer for Check Your Progress : |

|-----|----------------------------------|

|     | Check Your Progress 1 :          |

|     | See Section 1.2.2                |

|     | Check Your Progress 2 :          |

|     | See Section 1.3                  |

|     | Check Your Progress 3 :          |

|     | See Section 1.4                  |

|     | Check Your Progress 4 :          |

|     | See Section 1.5                  |

18

#### Check Your Progress 5 :

| 1 : See Section 1.6 | 2 : D | <b>3</b> : C |

|---------------------|-------|--------------|

| 4 : D               | 5 : A | 6 : A        |

| 7 : A               |       |              |

#### 1.9 Glossary :

- 1. Non–Positional Number Systems In early days, human beings counted on fingers. when ten fingers were not adequate, he made use of pebbles, stones etc. to indicate values. This method of counting uses and preservative approach or the non–positional number system.

- 2. **Positional Number Systems** In the positional number system, called points are only the few symbols and the symbols they correspond to different values depending on the state in the number. The value of each digit in such the number system is determined by three considerations.

- **3. Decimal Number System** The conventional number system used currently is the decimal number system. The decimal number system has the digits from 0 to 9 and the numbers have the base ten.

#### 1.10 Assignment :

- 1. What is the bit in computer terminology ? How many different patterns of bits are possible with it ?

- 5 bits

- 6 bits

- 7 bits

- 8 bits

- What will be the total number of different symbols or digits and the maximum value of the single digit for the following number systems? Number system with base 5 Number system with base 20 Number system with base 9 Number system with base 12

#### 1.11 Activities :

What is the difference between positional and non-positional number system.

Write examples of both types of number system.

#### 1.12 Case Study :

What is the base of the number system? Write examples to illustrate the role of base in positional number systems

| 1.1 | 3 Further Reading :                            |

|-----|------------------------------------------------|

| 1.  | Digital Logic and Computer Design, Morris Mano |

2. Digital Electronics, Anand Kumar

# **COMPUTER ARITHMETIC**

### UNIT STRUCTURE

- 2.0 Learning Objectives

- 2.1 Introduction

- 2.2 Fractional Numbers

- 2.3 9's and 10's Complement

- 2.4 1's and 2's Complement

- 2.5 Representation of Negative Numbers

- 2.6 Let Us Sum Up

- 2.7 Suggested Answer for Check Your Progress

- 2.8 Glossary

- 2.9 Assignment

- 2.10 Activities

- 2.11 Case Study

- 2.12 Further Readings

#### 2.0 Learning Objectives :

#### After learning this unit, you will be able to :

- Perform Fractional number representation

- Represent negative numbers

- Perform subtraction

- Explain 1's complement

- Discuss 2's complement

#### 2.1 Introduction :

In the computer system, data is stored in the format that cannot be simply understood by human beings. This is the cause why input and output (I/O) interfaces are essential. Each computer stores letters, numbers and the special characters in the coded form. Before going into the details of these codes, it is essential to have the basic understanding of the number system. It also introduces some of the commonly used number systems by computer professionals and the relationship between them.

This chapter deals with the basic fundamentals of number system, computer arithmetic and binary codes. Data in the computer is stored in the series of bits which are often interpreted in blocks known as bytes [8 bits] or words. The ALU (Arithmetic and Logic Unit) performs arithmetic operations on data and the control unit needs to 'decode' instructions. Both of these jobs are performed by logic circuits.

#### 2.2 Fractional Numbers :

In binary number system, fractional numbers are formed in the same general way as in the decimal system. The fraction in decimal number system can be represented as :

$$\begin{array}{l} 0.235 = (2 \times 10^{-1}) + (3 \times 10^{-2}) + (5 \times 10^{-3}) \text{ And} \\ 68.53 = (6 \times 10^{1}) + (8 \times 10^{0}) + (5 \times 10^{-1}) + (3 \times 10^{-2}) \\ \text{Similarly in the binary system,} \\ 0.101 = (1 \times 2^{-1}) + (0 \times 2^{-2}) + (1 \times 2^{-3}) \\ \text{And} \end{array}$$

$10.01 = (1 \times 2^{1}) + (0 \times 2^{0}) + (0 \times 2^{-1}) + (1 \times 2^{-2})$

Therefore, the binary point as the decimal point serves the same purpose.

Some of positional values in binary systems are accurate.

**Binary Point**

| Position    | 4  | 3              | 2  | 1  | 0              | -1  | -2  | -3  | -4   |

|-------------|----|----------------|----|----|----------------|-----|-----|-----|------|

| Value       | 24 | 2 <sup>3</sup> | 22 | 21 | 2 <sup>0</sup> | 2-1 | 2-2 | 2-3 | 2-4  |

| Represented | 16 | 8              | 4  | 2  | 1              | 1/2 | 1/4 | 1/8 | 1/16 |

In common, the number in the number system with base b would be written as :

The symbols  $a_n a_{n-1}$ , ...,  $a_{-m}$  used in The above representation should be one of The symbols allowed in The number system. Thus, as per the above mentioned general rule,

$$46.328 = (4 \times 8^{1}) + (6 \times 8^{0}) + (3 \times 8^{-1}) + (2 \times 8^{-2})$$

and

$$5A.3C_{16} = (5 \times 16^{1}) + (A \times 16^{0}) + (3 \times 16^{-1}) + (C \times 16^{-2})$$

Example - 1 :

Find the decimal equivalent of the binary number 110.101

#### Solution :

$$110.101_{2} = 1 \times 2^{2} + 1 \times 2^{1} + 0 \times 2^{0} + 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3}$$

$$= 4 + 2 + 0 + .5 + 0 + .125$$

$$= 6 + 0.5 + 0.125$$

$$= 6.625_{10}$$

#### Example – 2 :

Find the decimal equivalent of the octal number 127.54

### Solution : $127.548 = 1 \times 8^2 + 2 \times 8^1 + 7 \times 8^0 + 5 \times 8^{-1} + 4 \times 8^{-2}$

$$= 64 + 16 + 7 + 5/8 + 4/64$$

= 87 + 0.625 + 0.0625

= 87.6875<sub>10</sub>

#### Example – 3 :

Find the decimal equivalent of the hexadecimal number 2B.C4

#### Solution :

```

2B.C4_{16} = 2 \times 16^{1} + B \times 16^{0} + C \times 16^{-1} + 4 \times 16^{-2}

= 32 + 11 + C/16 + 4/256

= 43 + 0.75 + 0.015625

= 43.765652_{10}

```

#### □ Check Your Progress – 1 :

1. Explain 'Fractional Numbers'

# The 9's complement is used to find the subtraction of the decimal numbers. The 9's complement of a number is calculated by subtracting each digit of the number by 9. 9's and 10's complement in the decimal number system

#### 9's complement

are dealt with for better understanding.

To obtain 9's complement of the decimal number each digit of the number is subtracted from 9. For example, 9's complement of 45 is (99 - 45) = 54

9's complement of 523 = (999 - 523) = 476

The 10's complement is also used to find the subtraction of the decimal numbers. The 10's complement of a number is calculated by subtracting each digit by 9 and then adding 1 to the result. Simply, by adding 1 to its 9's complement we can get its 10's complement value.

10's complement

10's complement of the decimal number = its 9's complement + 1.

10's complement of 45 = 54 + 1 = 55

10's complement of 523 = 476 + 1 = 477

On adding the number 45 and its 10's complement, the sum becomes zero (omitting the carry over)

#### Example – 4 :

|      | -      |   |                       |

|------|--------|---|-----------------------|

| 4    |        | 5 | (decimal number)      |

|      | ~      | ~ |                       |

| +    | 5      | 5 | (its 10's complement) |

| 0    |        | 0 |                       |

| 0    |        | 0 |                       |

| Car  | ry = 1 |   |                       |

| Carr | iy i   |   |                       |

In this case the decimal number is of two digits. If the sum of the number and its 10's complement only up to two digits are considered, the sum becomes zero. Similarly,

| Example – 5 : |           |   |   |                       |  |

|---------------|-----------|---|---|-----------------------|--|

|               | 5         | 2 | 3 | (decimal number)      |  |

| +             | 4         | 7 | 7 | (its 10's complement) |  |

|               | 0         | 0 | 0 |                       |  |

|               | Carry = 1 |   |   |                       |  |

The decimal number 523 is of three digits. Considering The sum of the number and its 10's complement only up to three digits, the sum becomes zero. Thus it is concluded that 10's complement gives the negative value of the number

10's complement of the decimal number = – decimal number 1's Complement

#### □ Check Your Progress – 2 :

1. Explain 9's and 10's complement

2. Find 9's Complement of 67.

3. Find 10's Complement of 67.

#### 2.4 1's and 2's Complement :

#### **Computer Arithmetic**

1's complement in the binary number system is similar to The 9's complement in the decimal system. 1's complement of the binary number is obtained by subtracting each bit of the number from 1. 1's complement of 01 is 10. 1's complement of 111 is 000. Thus, 1's complement of the binary number can be obtained by simply changing bit 1 to 0 and 0 to 1.

#### Example – 6 :

```

Find 1's complement of 100110

1's complement of 100110 = 011001

Example - 7 :

Find 1's complement of 0000

1's complement of 0000 = 1111

Example - 8 :

Find 1's complement of 11111

1's complement of 11111

1's complement of 11111

2's Complement.

```

2's complement in the binary number system is similar to 10's complement in the decimal number system. 2's complement of binary number = its 1's complement + 1.

#### Example – 9 :

```

Find 2's complement of 10011

2's complement of 10011 = 01100 + 1 = 01101

Example - 10 :

Find 2's complement of 111.

2's complement of 111 = 000 + 1 = 001

Example – 11 :

Find 2's complement of 0000

2's complement of 0000 = 1111 + 1 = 0000

Consider the case of adding the binary number to its 2's complement.

Example – 12 :

Binary number

= 1001

Its 1's complement = 0110

Its 2's complement = 0110 + 1 = 0111.

Number + its 2's complement

1

0

0

1

=

1

0

1

1

0

0

0

0

Carry =1

```

The last carry is lost if the processor is of 4 bits or only 4 bits sum is considered. For 8-bit processor the number and 2's complement will be written in 8 bits as given below :

| Number           | = 00001001     |

|------------------|----------------|

| 1's complement   | = 11110110     |

| 2's complement   | = 11110110 + 1 |

|                  | = 11110111     |

| Number           | = 00001001     |

| + 2's complement | = 11110111     |

|                  | 0000000        |

|                  | Carry = 1      |

The last carry will be neglected, if The 8 bit sum is considered.

| Example – 13 :          |                |          |

|-------------------------|----------------|----------|

| + 4 (decimal)           | = 00000100     | (binary) |

| -4 = Its 2's complement | = 11111011 + 1 |          |

|                         | = 11111100     |          |

| +4                      | = 00000100     |          |

| -4                      | = 11111100     |          |

|                         | 00000000       |          |

Example – 14 :

Addition

Add + 5 and -7

7 = 00000111 -7 = 11111000 + 1 = 11111001 +5 = 00000101 -7 = 11111001 -2 = 11111100Check : 2 = 00000010 -2 = 11111101 + 1= 11111110

Thus, 2's complement of the binary number represents its negative.

Binary Subtraction Using 2's Complement

Addition of 2's complement of the number is equivalent to the subtraction of the number.

Suppose, 0010 (2 decimal) has to be subtracted from 0101 (5 decimal). If the 2's complement of 0010 (2 decimal) is added to 0101 (5 decimal) the sum will be 0011 (3 decimal). It is equal to 0101 (5 decimal) – 0010 (2 decimal) = 0011 (3 decimal).

Ordinary binary subtraction :

| 0101   | (5 decimal)  |

|--------|--------------|

| - 0010 | (-2 decimal) |

| 0011   | (3 decimal)  |

Subtraction using 2's complement :

1's complement of 0010 (2 decimal) = 1101

2's complement of 0010 = 1101 + 1 = 1110

- 0101 (5 decimal)

- + 1110 (+ 2's complement of 2)

- 0011 (3 decimal)

The carry of the last stage is neglected.

#### □ Check Your Progress – 3 :

1. Explain 2's complement using example.

#### 2.5 Representation of Negative Numbers :

2's complement is used to represent the negative of the binary number.

For example to represent -4, First write binary representation of 4, so it is 00000100. Its 1's complement is 11111011. Then add 1 to resultant number to find 2's complement.

11111011 + 1 = 11111100

#### Example – 15 :

| + 4 (decimal)           | = 00000100 (binary) |

|-------------------------|---------------------|

| -4 = Its 2's complement | = 11111011 + 1      |

|                         | = 11111100          |

| +4                      | = 00000100          |

| -4                      | = 11111100          |

|                         | 00000000            |

1

#### Example - 16 :

Addition

Add + 5 and -7

$$7 = 00000111$$

$$-7 = 11111000 + 1$$

$$= 11111001$$

$$+5 = 00000101$$

$$-7 = 11111001$$

$$-2 = 11111100$$

Check : 2 = 00000010

$$-2 = 11111101 +$$

$$= 11111110$$

Thus, 2's complement of the binary number represents its negative.

Binary Subtraction Using 2's Complement

Addition of 2's complement of the number is equivalent to the subtraction of the number. Suppose, 0010 (2 decimal) has to be subtracted from 0101 (5 decimal). If the 2's complement of 0010 (2 decimal) is added to 0101 (5 decimal) the sum will be 0011 (3 decimal). It is equal to 0101 (5 decimal) - 0010 (2 decimal) = 0011 (3 decimal).

Ordinary binary subtraction :

| 0101                                                          |                                                   |                                                                            |                                                            |                            |

|---------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------|----------------------------|

| 0101                                                          | (5 deci                                           | imal)                                                                      |                                                            |                            |

| -0010                                                         | (-2 de                                            | cimal)                                                                     |                                                            |                            |

| 0011                                                          | (3 dec                                            | imal)                                                                      |                                                            |                            |

| Subtrac                                                       | tion usin                                         | ng 2's compleme                                                            | nt:                                                        |                            |

| 1's com                                                       | nplement                                          | of 0010 (2 dec                                                             | imal) = 1101                                               |                            |

| 2's com                                                       | nplement                                          | of 0010                                                                    | = 1101 +                                                   | 1 = 1110                   |

| 0                                                             | 101 (5 a                                          | decimal)                                                                   |                                                            |                            |

| + 1                                                           | 110 (+ 2                                          | 2's complement                                                             | of 2)                                                      |                            |

| 0                                                             | 011 (3 a                                          | decimal)                                                                   |                                                            |                            |

|                                                               |                                                   | e last stage is r                                                          | neglected.                                                 |                            |

| Check                                                         | Your Pr                                           | rogress – 4 :                                                              |                                                            |                            |

| Explain                                                       | how to                                            | represent negat                                                            | ive numbers in bi                                          | nary system ?              |

|                                                               |                                                   |                                                                            |                                                            | ·····                      |

|                                                               |                                                   |                                                                            |                                                            |                            |

|                                                               |                                                   |                                                                            |                                                            |                            |

|                                                               |                                                   |                                                                            |                                                            |                            |

|                                                               |                                                   |                                                                            |                                                            |                            |

|                                                               |                                                   |                                                                            |                                                            |                            |

| Subtrac                                                       | t 0011 f                                          | rom 1110 using                                                             | ordinary and bina                                          | ary subtraction.           |

| Subtrac                                                       | t 0011 f                                          | rom 1110 using                                                             | ordinary and bina                                          | ary subtraction.           |

| Subtrac                                                       | t 0011 f                                          | rom 1110 using                                                             | ordinary and bina                                          | ary subtraction.           |

| Subtrac                                                       | t 0011 f                                          | rom 1110 using                                                             | ordinary and bina                                          | ary subtraction.           |

| Subtrac                                                       | t 0011 f                                          | rom 1110 using                                                             | ordinary and bina                                          | ary subtraction.           |

| Subtrac                                                       |                                                   |                                                                            | ordinary and bina                                          | -                          |

|                                                               |                                                   |                                                                            |                                                            | -                          |

| 1's com                                                       | nplement                                          | of 1011101 is '                                                            |                                                            |                            |

| 1's con<br>(a) 010                                            | nplement<br>1110                                  | of 1011101 is '                                                            | ?<br>(c) 0100010                                           |                            |

| 1's con<br>(a) 010<br>2's con                                 | nplement<br>1110<br>nplement                      | of 1011101 is<br>(b) 1001101<br>of 11001011 is                             | ?<br>(c) 0100010                                           | (d) 1100101                |

| 1's com<br>(a) 010<br>2's com<br>(a) 010                      | nplement<br>11110<br>nplement<br>10111            | of 1011101 is<br>(b) 1001101<br>of 11001011 is                             | ?<br>(c) 0100010<br>                                       | (d) 1100101                |

| 1's com<br>(a) 010<br>2's com<br>(a) 010<br>9's com           | nplement<br>11110<br>nplement<br>10111            | of 1011101 is<br>(b) 1001101<br>of 11001011 is<br>(b) 11010100<br>of 33 is | ?<br>(c) 0100010<br>                                       | (d) 1100101                |

| 1's com<br>(a) 010<br>2's com<br>(a) 010<br>9's com<br>(a) 99 | nplement<br>1110<br>nplement<br>10111<br>nplement | of 1011101 is<br>(b) 1001101<br>of 11001011 is<br>(b) 11010100<br>of 33 is | ?<br>(c) 0100010<br>(c) 00110101<br>(c) 00110101<br>(c) 44 | (d) 1100101<br>(d) 1110001 |

22

7. 10's complement of 3336 is \_\_\_\_\_ ? (a) 6664 (b) 6663 (c) 6666 (d) 3336

**2.6 Let Us Sum Up :** Fractional numbers are formed in the same way as in decimal number

system. In general the number in the number system having base b would be express as :  $a_n = a_{n-1} \dots a_1 = a_0 = a_{-1} \dots a_{-m}$

And would be interpreted to mean

The symbols  $a_n a_{n-1}$ , ...,  $a_{-m}$  used in the above depiction should be one of the symbols approved in the number system. Thus, as per the above mentioned general rule the techniques for following types of conversions to convert numbers from one base to another base should be known.

Converting from another base to decimal

Converting from decimal to another base

The negative numbers in binary system are represented using 2's complement.

#### 2.7 Answer for Check Your Progress :

|     | Check Your Progress 1 : |              |          |

|-----|-------------------------|--------------|----------|

|     | See Section 2.2         |              |          |

|     | Check Your Progress 2 : |              |          |

|     | See Section 2.3         |              |          |

|     | Check Your Progress 3 : |              |          |

|     | See Section 2.4         |              |          |

|     | Check Your Progress 4 : |              |          |

|     | 1 : See Section 2.5     | 2 : See Sect | tion 2.5 |

|     | <b>3</b> : C            | <b>4</b> : C | 5 : B    |

|     | <b>6</b> : B            | 7 : A        |          |

| 2.8 | <b>Glossary</b> :       |              |          |

1. 1's complement : It is used for binary system. In this 0 is replaced by 1 and 1 is replaced by 0.

2. 2's complement : It is used to represent negative numbers in binary system. If we add1 to 1's complement of any number it gives 2,s complement.

#### 2.9 Assignment :

- 1. Find 9's complement of 56.

- 2. Find 10's complement of 56.

- 3. Find 1's complement of 0001

- 4. Find 2's complement of 0001

- 5. Compare 10's complement with 2's complement.

#### 2.10 Activities :

In which case we can apply 1's complement ? Any alternative method exists which can use to represent 2's complement?

#### 2.11 Case Study :

List all applications of 2's complement

#### 2.12 Further Reading :

- 1. Digital Logic and Computer Design, Morris Mano

- 2. Digital Electronics, Anand Kumar

Unit **03**

# CODES FOR CHARACTER REPRESENTATION

### UNIT STRUCTURE

- 3.0 Learning Objective

- 3.1 Introduction

- 3.2 Binary Coded Decimal

- 3.3 Excess 3 Code

- 3.4 Gray Code

- 3.5 Let Us Sum Up

- 3.6 Answers for Check Your Progress

- 3.7 Glossary

- 3.8 Assignment

- 3.9 Activities

- 3.10 Case studies

- 3.11 Further Readings

#### 3.0 Learning Objectives :

After learning this unit, you will be able to :

- Define BCD

- Define Excess–3 Code

- Define Gray code

#### 3.1 Introduction :

Electronic systems use signals have two distinct values and circuit element have two stable states. There is a direct analogy among signals and binary digits. In this section we will focus on some different representation of binary system like BCD, Excess 3 code and Gray code which used in computer system architecture.

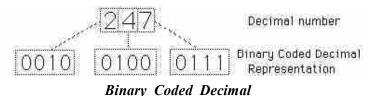

#### 3.2 Binary Coded Decimal :

One of The most widely used representations of numerical data is the binary coded decimal (BCD) form, in which the4–bit binary number represents each integer of the decimal number. It is particularly useful for the driving of display devices where the decimal output is desired. BCD usually refers to such coding in which binary digits have their normal values, that is, 8421. Sometimes it is written '8421 BCD' to clearly distinguish it from other binary codes such as The 4221 Code, but when BCD is used without qualification, The 8421 version is assumed.

The following table gives the decimal number along with Their BCD codes.

| Decimal Number | Standard BCD Number |

|----------------|---------------------|

| 0              | 0000                |

| 1              | 0001                |

| 2              | 0010                |

| 3              | 0011                |

| 4              | 0100                |

| 5              | 0101                |

| 6              | 0110                |

| 7              | 0111                |

| 8              | 1000                |

| 9              | 1001                |

| 10             | 00010000            |

| 11             | 00010001            |

| 12             | 00010010            |

| 13             | 00010011            |

| 14             | 00010100            |

| 30             | 00110000            |

| 45             | 01000101            |

| 64             | 01100100            |

| 73             | 01110011            |

| 98             | 10011000            |

Table 3.1 : Decimal to Standard BCD Conversion

### **\*** Alphanumeric Coding :

For the inherently binary world of the computer, it is necessary to put all symbols, letters, numbers, etc. into binary form. The most commonly used alphanumeric code is the ASCII code, with others like the EBCDIC code being applied in some communication applications.

### □ Check Your Progress – 1 :

1. Explain Binary Coded Decimal with example.

### 3.3 Excess-3 Code :

The excess-3 code (or XS3) is a non-weighted code used to express code used to direct decimal numbers. It is a self-complementary binary coded decimal (BCD) code which has biased representation. It is particularly significant for arithmetic operations as it overcomes inadequacy encountered while using 8421 BCD code to add two decimal digits whose sum exceeds 9.

#### Representation of Excess-3 Code :

Excess–3 codes are unweighted and can be obtained by adding 3 to each decimal digit then it can be represented by using 4 bit binary number for each digit. An Excess–3 equivalent of a given binary binary number is obtained using the following steps:

- Find the decimal equivalent of the given binary number.

- Add +3 to each digit of decimal number.

- Convert the newly obtained decimal number back to binary number to get required excess-3 equivalent.

You can add 0011 to each four-bit group in binary coded decimal number (BCD) to get desired excess-3 equivalent.

| Decimal | BCD Code | Excess 3 Code |

|---------|----------|---------------|

| 0       | 0000     | 0011          |

| 1       | 0001     | 0100          |

| 2       | 0010     | 0101          |

| 3       | 0011     | 0110          |

| 4       | 0010     | 0111          |

| 5       | 0101     | 1000          |

| 6       | 0110     | 1001          |

| 7       | 0111     | 1010          |

| 8       | 1000     | 1011          |

| 9       | 1001     | 1100          |

These are following excess-3 codes for decimal digits -

Note : codes 0000 and 1111 are not used for any digit.

Example – 1 : Convert decimal number 23 to Excess–3 code.

So, according to excess-3 code we need to add 3 to both digit in the decimal number then convert into 4-bit binary number for result of each digit. Therefore,

= 23 + 34 = 56 = 01010110 which is required excess-3 code for given decimal number 23.

Example – 2 : Convert decimal number 15.46 into Excess-3 code.

According to excess–3 code we need to add 3 to both digit in the decimal number then convert into 4–bit binary number for result of each digit. Therefore,

$= 15.46 + 33.33 = 48.79 = 0100 \ 1000.0111 \ 1001$  which is required excess-3 code for given decimal number 15.46.

Digital Electronics and

**Computer Organization**

### Check Your Progress – 2 :

1. Explain Excess-3 code on detail. Explain the issues with BCD which can be overcome with Excess-3 code.

### 3.4 Gray Code :

The reflected binary or Gray Code is shown in Table 3.2. In this code only one bit changes in the transition from one number to the next higher number. The Gray code is used in shaft encoder, which is to indicate the angular position of the shaft. The use of Gray code reduces errors.

Suppose that the present position of the shaft is indicated by Gray code 0100, which is for 7. If the position changes to 8, the Gray code will be 1100. If the detector does not pick up the encoder the new change in binary bit will show the previous position that is 7. However, in case of ordinary binary code, 7 is represented by 0111 and 8 by 1000.

Now suppose the detector picks up the least significant bits, that is, 000, but fails to pick up the most significant bit 1, the output will be 0000 instead of 1000. So there is the large error if the simple binary code is used for the shaft encoder.

| Decimal | Binary Code | Gray Code |

|---------|-------------|-----------|

| 0       | 0000        | 0000      |

| 1       | 0001        | 0001      |

| 2       | 0010        | 0011      |

| 3       | 0011        | 0010      |

| 4       | 0100        | 0110      |

| 5       | 0101        | 0111      |

| 6       | 0110        | 0101      |

| 7       | 0111        | 0100      |

| 8       | 1000        | 1100      |

| 9       | 1001        | 1101      |

| 10      | 1010        | 1111      |

| 11      | 1011        | 1110      |

| 12      | 1100        | 1010      |

| 13      | 1101        | 1011      |

| 14      | 1110        | 1001      |

| 15      | 1111        | 1000      |

Table 3.2 : Grav Code

| Check Your Pr                                      | ogress – 3 :         |                     |                     |

|----------------------------------------------------|----------------------|---------------------|---------------------|

| Explain Gray Co                                    | ode.                 |                     |                     |

|                                                    |                      |                     |                     |

|                                                    |                      |                     |                     |

|                                                    |                      |                     |                     |

|                                                    |                      |                     |                     |

|                                                    |                      |                     |                     |

| Why do we use                                      |                      |                     |                     |

|                                                    | e no of bits chan    | iges                |                     |

| (b) To rotate a                                    | shaft                |                     |                     |

| (c) Error correct                                  | tion                 |                     |                     |

| (d) To count the                                   | e no of bits chan    | nges and To rota    | ate a shaft         |

| (e) None of the                                    | Mentioned            |                     |                     |

| The binary repr                                    | esentation of BC     | D number 00101      | 001 (decimal 29) is |

| (a) 00011101                                       | (b) 0110101          | (a) 0000000         | (d) 11111110        |

| (a) 00011101<br>(e) None of the                    |                      | (c) 0000000         | (d) 11111110        |

|                                                    | s called a           |                     |                     |

| (a) bit                                            |                      | (c) number          | (J) A11             |

|                                                    |                      |                     | (u) All             |

|                                                    | equivalent of $(10)$ |                     | (d) 1111            |

| <ul><li>(a) 1101</li><li>(e) None of abc</li></ul> |                      | (c) 1110            | (d) 1111            |

|                                                    |                      |                     |                     |

| 85 in BCD code                                     |                      | (a) 1000 0101       | (d) 1101 1001       |

|                                                    | (b) 1101 1010        | (c) 1000 0101       | (d) 1101 1001       |

| (e) all of above                                   |                      | da 1110 ia          |                     |

|                                                    | valent of gray co    |                     |                     |

| (a) 1101                                           | (b) 1011             | (c) 1110            | (d) 1111            |

| The binary equi                                    | valent of gray co    | (c) 1110 $(c) 1110$ | (d) 1010            |

| (a) 1101                                           | (b) 1011             |                     |                     |

The different character representation codes we have reviewed in this section. They are very useful in computer architecture.

Machines can understand binary number system, some machines understand hexadecimal number system. But in case of signal and digital circuit binary number system is suitable as they have the same scenario like on -off ,0-1 and true-false. When dealing with binary number system, machines sometimes faces some issues. To overcome these some more codes are introduced, they are using only binary system that is 0 and 1 but representation is quite different.

| Digital Electronics and<br>Computer Organization | 3.6 Answer for Check Your Progress :                                                   |                                                                      |                         |                          |

|--------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------|--------------------------|

| Computer Organization                            | Check Your Progress 1 :                                                                |                                                                      |                         |                          |

|                                                  |                                                                                        | See Section 3.2                                                      |                         |                          |

|                                                  |                                                                                        | Check Your Progress 2 :                                              |                         |                          |

|                                                  |                                                                                        | See Section 3.3                                                      |                         |                          |

|                                                  |                                                                                        | Check Your Progress 3 :                                              |                         |                          |

|                                                  |                                                                                        | 1 : See Section 3.4                                                  | 2 : C                   | <b>3</b> : A             |

|                                                  |                                                                                        | <b>4</b> : A                                                         | 5 : C                   | <b>6</b> : C             |

|                                                  |                                                                                        | 7 : B                                                                | 8 : D                   |                          |

|                                                  | 3.7                                                                                    | Glossary :                                                           |                         |                          |

|                                                  | 1.                                                                                     | <b>BCD</b> : The binary–coded deci<br>numbers in which each digit is | . ,                     | •                        |

|                                                  | 2.                                                                                     | Gray Code : Gray code is an such that two successive value           | -                       |                          |

|                                                  | 3.8                                                                                    | 3.8 Assignment :                                                     |                         |                          |

|                                                  | <ol> <li>Explain the difference among BCD, Excess 3 code and G<br/>example.</li> </ol> |                                                                      | code and Gray code with |                          |

|                                                  | 2.                                                                                     | Generate Gray code for $n = 1$                                       | bit, $n = 2 b$          | its and $n = 3$ bits.    |

|                                                  | 3.9                                                                                    | Activities :                                                         |                         |                          |

|                                                  | 1.                                                                                     | Where is BCD code used ?                                             |                         |                          |

|                                                  | 2.                                                                                     | Where Gray Codes are used ?                                          |                         |                          |

|                                                  | 3. Where is Excess 3 code used ?                                                       |                                                                      |                         |                          |

|                                                  | 3.1                                                                                    | 0 Case Study :                                                       |                         |                          |

|                                                  | name                                                                                   | Refer the format of date and t<br>es of those PCs.                   | ime in BIOS of          | of Some PCs and list the |

|                                                  | 3.1                                                                                    | 1 Further Reading :                                                  |                         |                          |

|                                                  | 1.                                                                                     | Digital Logic and Computer D                                         | esign. Morris           | Mano                     |

- 1. Digital Logic and Computer Design, Morris Mano

- 2. Digital Electronics, Anand Kumar

### **BLOCK SUMMARY :**

Number systems are of two types-non positional and positional. In the non-positional number system, every symbol represents the same value apart from of its position in the number and to find the value of the number, one has to count the number of symbols present in the number. It is enormously difficult to perform arithmetic with such the number system. In the positional number system there are only the little symbols called digits. These symbols represent different values depending on the position they occupy in the number. The value of every digit in such the number is determined by three considerations.

- a. The digit itself

- b. The position of the digit in the number

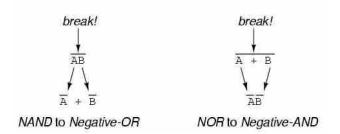

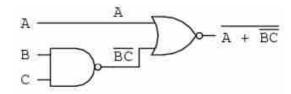

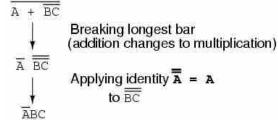

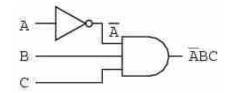

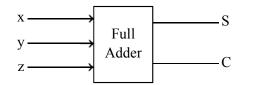

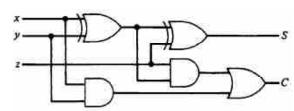

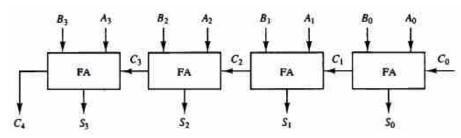

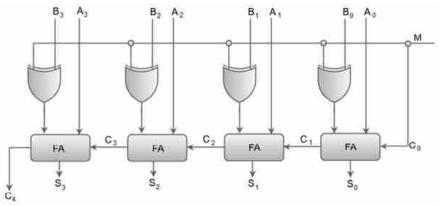

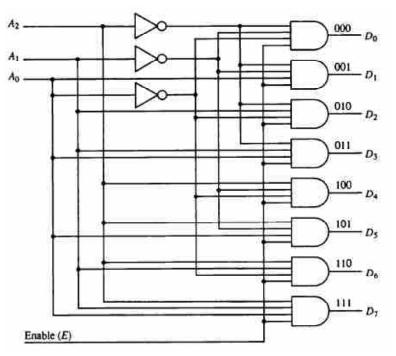

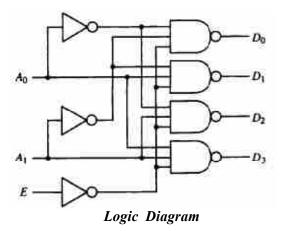

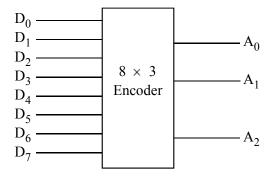

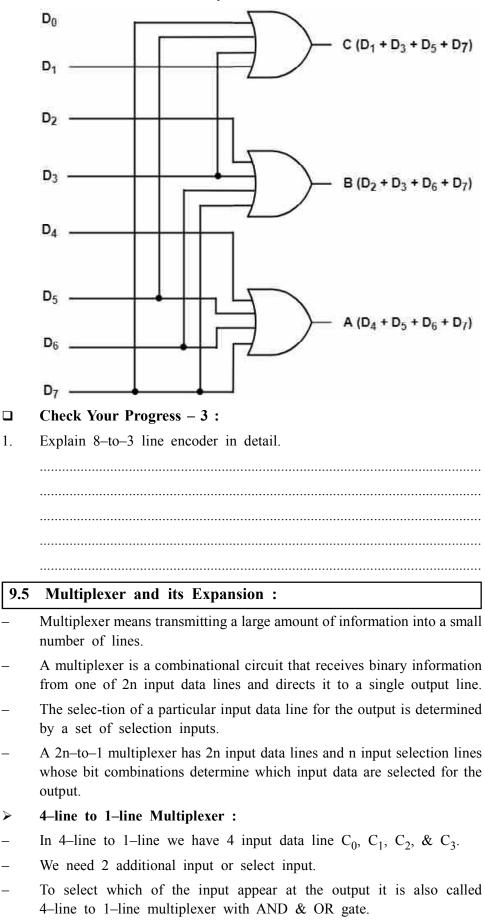

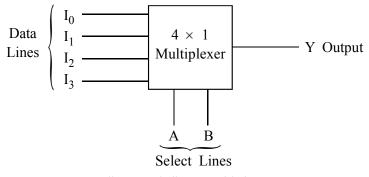

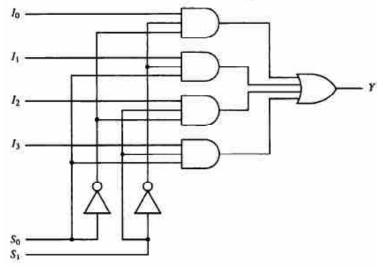

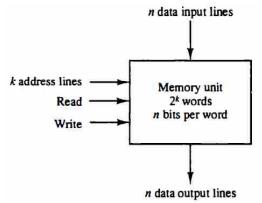

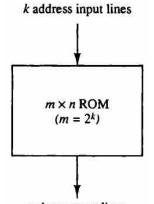

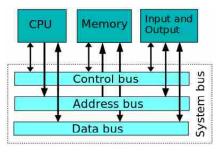

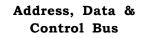

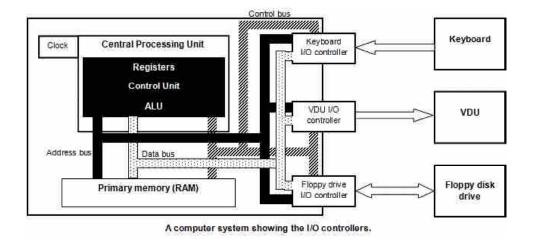

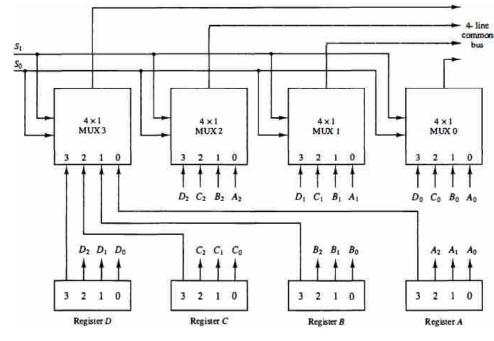

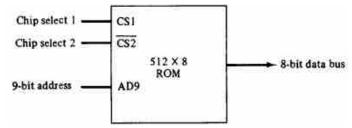

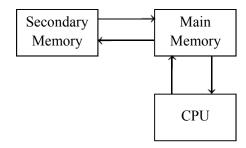

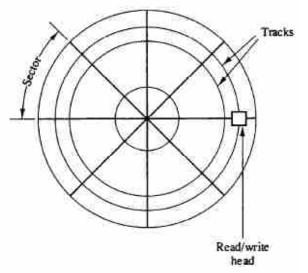

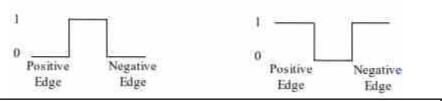

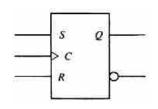

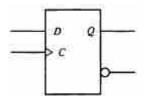

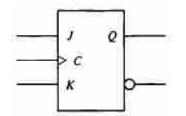

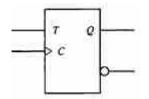

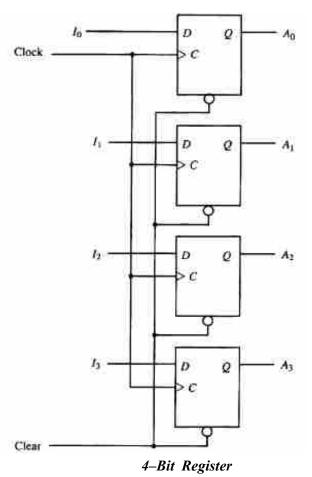

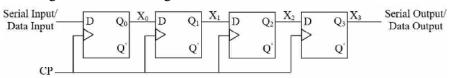

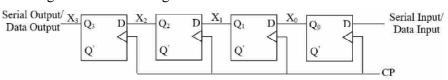

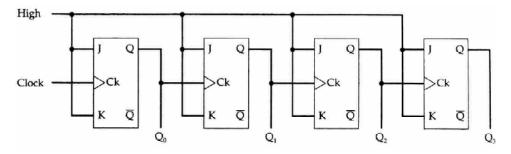

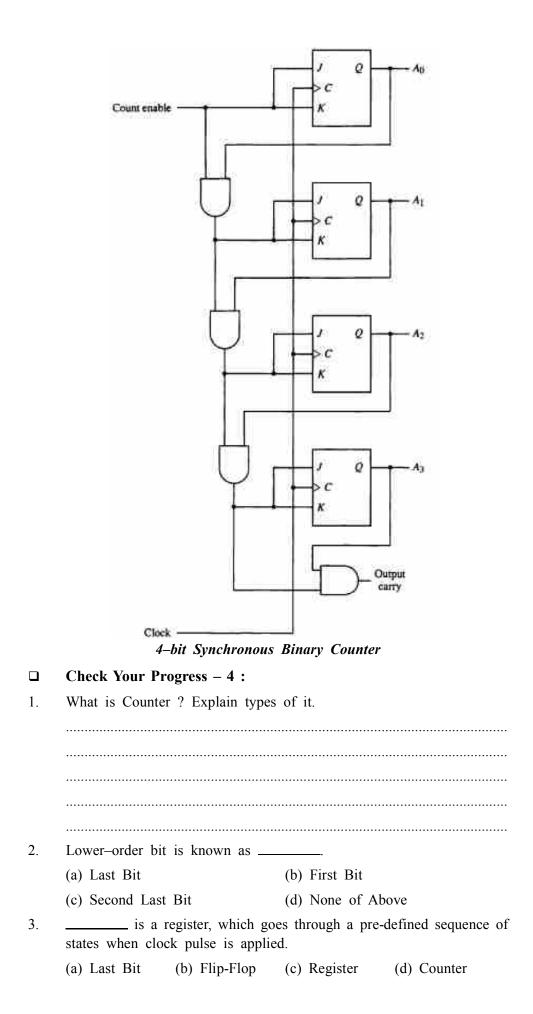

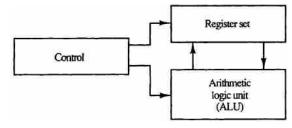

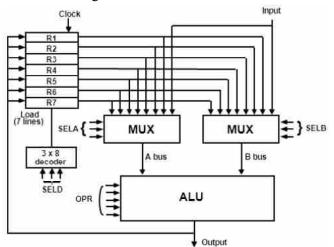

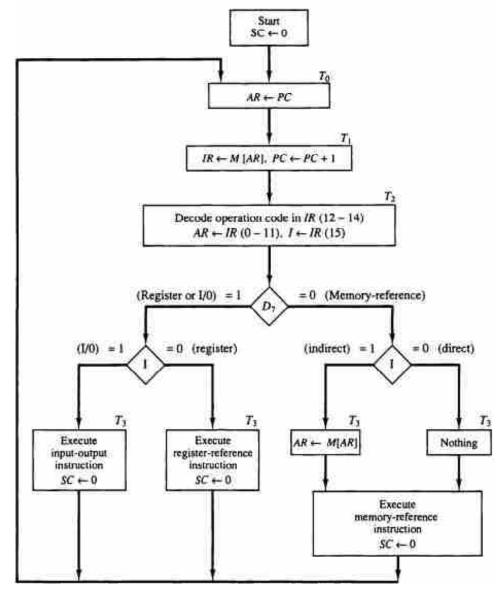

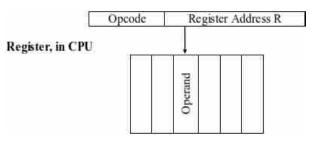

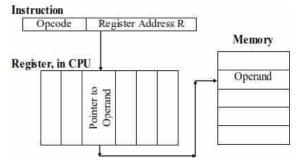

- c. The base of the number system