## DR.BABASAHEB AMBEDKAR OPEN UNIVERSITY

# BCA

### **BACHELOR OF COMPUTER APPLICATION**

**BCAR-303**

**System Programming and Introduction to Microprocessor**

## SYSTEM PROGRAMMING AND INTRODUCTION TO MICROPROCESSOR

DR. BABASAHEB AMBEDKAR OPEN UNIVERSITY

AHMEDABAD

#### **Editorial Panel**

Authors : Amit Suthar

Assistant Professor,

AMPICS | Department of Computer Science,

Ganpat University - Kherva.

Amit Bardhan

Assistant Professor,

Som-Lalit Education & Research Foundation,

Computer Science Department,

Opp. St. Xavier's College, Navrangpura Ahmedabad.

Editor : Mr. Parimal Patel

I/C Director,

Khyati School of Computer Application,

Ahmedabad.

Language Editor: Dr. Vasant K. Joshi

Associate Professor,

G. B. Shah Commerce College,

Ahmedabad

ISBN 978-93-91071-08-0

Edition: 2021

### Copyright $\odot$ 2021 Knowledge Management and Research Organisation.

All rights reserved. No part of this book may be reproduced, transmitted or utilized in any form or by a means, electronic or mechanical, including photocopying, recording or by any information storage or retrieval system without written permission from us.

### Acknowledgment

Every attempt has been made to trace the copyright holders of material reproduced in this book. Should an infringement have occurred, we apologize for the same and will be pleased to make necessary correction/amendment in future edition of this book.

The content is developed by taking reference of online and print publications that are mentioned in Bibliography. The content developed represents the breadth of research excellence in this multidisciplinary academic field. Some of the information, illustrations and examples are taken "as is" and as available in the references mentioned in Bibliography for academic purpose and better understanding by learner.

## ROLE OF SELF-INSTRUCTIONAL MATERIAL IN DISTANCE LEARNING

The need to plan effective instruction is imperative for a successful distance teaching repertoire. This is due to the fact that the instructional designer, the tutor, the author(s) and the student are often separated by distance and may never meet in person. This is an increasingly common scenario in distance education instruction. As much as possible, teaching by distance should stimulate the student's intellectual involvement and contain all the necessary learning instructional activities that are capable of guiding the student through the course objectives. Therefore, the course / self-instructional material are completely equipped with everything that the syllabus prescribes.

To ensure effective instruction, a number of instructional design ideas are used and these help students to acquire knowledge, intellectual skills, motor skills and necessary attitudinal changes. In this respect, students' assessment and course evaluation are incorporated in the text.

The nature of instructional activities used in distance education self-instructional materials depends on the domain of learning that they reinforce in the text, that is, the cognitive, psychomotor and affective. These are further interpreted in the acquisition of knowledge, intellectual skills and motor skills. Students may be encouraged to gain, apply and communicate (orally or in writing) the knowledge acquired. Intellectual–skills objectives may be met by designing instructions that make use of students' prior knowledge and experiences in the discourse as the foundation on which newly acquired knowledge is built.

The provision of exercises in the form of assignments, projects and tutorial feedback is necessary. Instructional activities that teach motor skills need to be graphically demonstrated and the correct practices provided during tutorials. Instructional activities for inculcating change in attitude and behavior should create interest and demonstrate need and benefits gained by adopting the required change. Information on the adoption and procedures for practice of new attitudes may then be introduced.

Teaching and learning at a distance eliminates interactive communication cues, such as pauses, intonation and gestures, associated with the face—to—face method of teaching. This is particularly so with the exclusive use of print media. Instructional activities built into the instructional repertoire provide this missing interaction between the student and the teacher. Therefore, the use of instructional activities to affect better distance teaching is not optional, but mandatory.

Our team of successful writers and authors has tried to reduce this.

Divide and to bring this Self Instructional Material as the best teaching and communication tool. Instructional activities are varied in order to assess the different facets of the domains of learning.

Distance education teaching repertoire involves extensive use of self-instructional materials, be they print or otherwise. These materials are designed to achieve certain pre-determined learning outcomes, namely goals and objectives that are contained in an instructional plan. Since the teaching process is affected

over a distance, there is need to ensure that students actively participate in their learning by performing specific tasks that help them to understand the relevant concepts. Therefore, a set of exercises is built into the teaching repertoire in order to link what students and tutors do in the framework of the course outline. These could be in the form of students' assignments, a research project or a science practical exercise. Examples of instructional activities in distance education are too numerous to list. Instructional activities, when used in this context, help to motivate students, guide and measure students' performance (continuous assessment)

### **PREFACE**

We have put in lots of hard work to make this book as userfriendly as possible, but we have not sacrificed quality. Experts were involved in preparing the materials. However, concepts are explained in easy language for you. We have included many tables and examples for easy understanding.

We sincerely hope this book will help you in every way you expect.

All the best for your studies from our team!

## SYSTEM PROGRAMMING AND INTRODUCTION TO MICROPROCESSOR

Contents

### **BLOCK 1: SYSTEM PROGRAMMING AND ASSEMBLY LANGUAGE**

## Unit 1 INTRODUCTION TO SYSTEM PROGRAMS AND SYSTEM PROGRAMMING

Introduction, Components of System Programming, Evolution of Operating Systems

### Unit 2 ELEMENTS OF ASSEMBLY LANGUAGE PROGRAMMING

Introduction, Programming Languages, 8085 Assembly Language

### Unit 3 ASSEMBLERS

Introduction, Functions of Assembler, Architecture of Assembler

### Unit 4 THE MACRO PROCESSOR AND LOADERS

Introduction, Macro Instructions, Macro Processor, Loaders

### **BLOCK 2: INTRODUCTION TO MICROPROCESSOR**

### Unit 5 INTRODUCTION TO MICROPROCESSOR

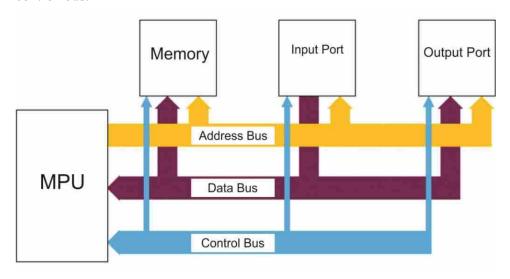

Introduction, Microprocessors, Internal Architecture, Bus System Architecture

### Unit 6 HISTORY AND OVERVIEW OF MICROPROCESSORS

Introduction, Intel 8085 Processing Architecture, SSI, MSI, VLSI, History of Microprocessors and Microcomputers

### Unit 7 THE 8085 MICROPROCESSOR

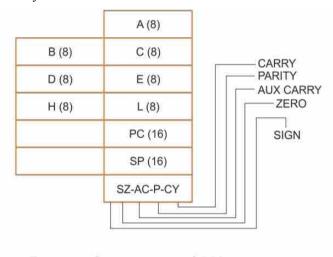

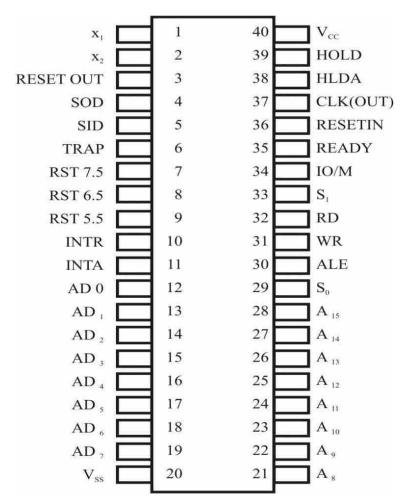

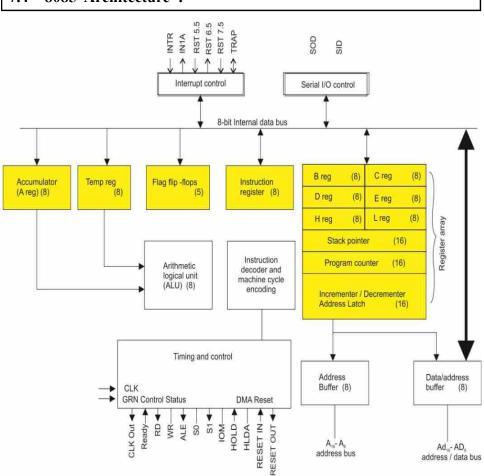

Introduction, 8085 Microprocessors, Registers in 8085, 8085 Architecture

### BLOCK 3: 8085, 8086/8088 PROGRAMMING, MULTIPROCESSOR CONFIGURATION

### Unit 8 INTERRUPTS

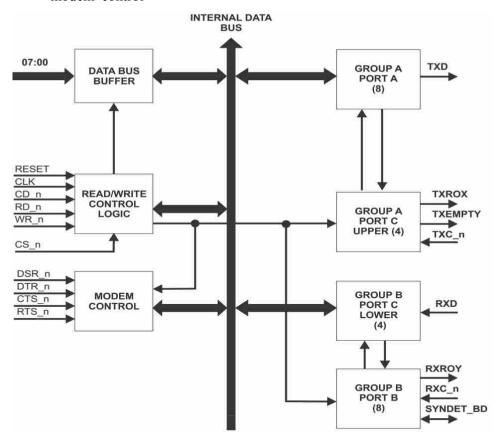

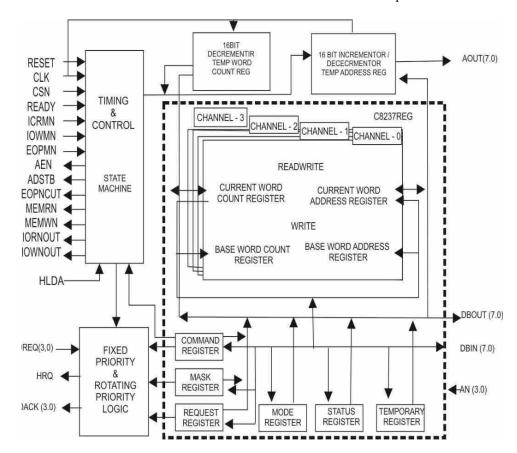

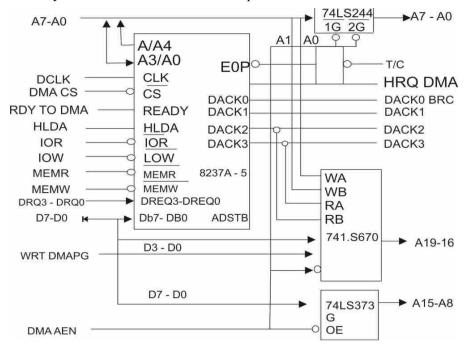

Introduction, 8085 Interrupts, 8259 : Programmable Interrupt Controller, 8251 : Programmable Communication Interface, Direct Memory Access (DMA)

### Unit 9 8085, 8086/8088 PROGRAMMING

Introduction, Addressing Modes, 8085 Instruction Set, 16 Bit Microprocessors

### Unit 10 MULTIPROCESSOR CONFIGURATION & MICROCONTROLLERS

Introduction, Coprocessor Configuration, Closely Coupled Configuration, Loosely Coupled Configuration, Microcontrollers, Types of Microcontrollers, Bit based configuration, Memory based configuration, Instruction set based configuration, Applications of Microcontrollers, Difference between Microprocessor and Micro-controller

### **BLOCK 4: MEMORY**

### Unit 11 MEMORY-I

Introduction, Primary Storage

### Unit 12 MEMORY-II

Introduction, Secondary Storage

### Unit 13 CACHE MEMORY ORGANIZATION

Introduction, Levels of Cache Memory, Measuring the Cache Performance, Cache Mapping, Direct Mapping, Associative Mapping, Set-Associative Mapping, Cache Coherance, Applications of Cache Memory, Locality of Reference

### Unit 14 OVERVIEW OF HIGHER VERSIONS

Introduction, Intel 80286, Intel 80386, Intel 80486, Intel Pentium

### BLOCK 1: SYSTEM PROGRAMMING AND ASSEMBLY LANGUAGE

- UNIT 1 INTRODUCTION TO SYSTEM PROGRAMS AND SYSTEM PROGRAMMING

- UNIT 2 ELEMENTS OF ASSEMBLY LANGUAGE PROGRAMMING

- UNIT 3 ASSEMBLERS

- UNIT 4 THE MACRO PROCESSOR AND LOADERS

## SYSTEM PROGRAMMING AND ASSEMBLY LANGUAGE

### **Block Introduction:**

In earlier days of computing, on/off switches were used as primitive devices for communication. To transfer information, system programs were developed to make computers better suited to the needs of users. Some of the system programs are operating systems, compilers, interpreters, loaders, linkers, macro processors etc.

In this block students will be aware of about system programming and its techniques with certain use of Assembly language. The students will find the block effective as it explains about operating programs and how one should be benefitted.

The block will detailed about system program and use of assembly language. The block will stress on 8085 Assembly Language, Assemblers, Macros and Macro processor and Loaders. The students will be trained with practical examples and exercises that will help to learn and grab the subject easily.

### **Block Objectives:**

### After learning this block, you will be able to understand:

- Components of System Programming

- Evolution of Operating Systems

- Programming Languages

- Idea about 8085 Assembly Language

- Study of Assemblers

- Knowledge about Macros and Macro processor

- Concept about Loaders

### **Block Structure:**

Unit 1: Introduction to System Programs and System

**Programming**

Unit 2 : Elements of Assembly Language Programming

Unit 3: Assemblers

Unit 4: The Macro Processor and Loaders

Unit **O1**

# INTRODUCTION TO SYSTEM PROGRAMS AND SYSTEM PROGRAMMING

### **UNIT STRUCTURE**

- 1.0 Learning Objectives

- 1.1 Introduction

- 1.2 Components of System Programming

- 1.3 Evolution of Operating Systems

- 1.4 Let Us Sum Up

- 1.5 Answers for Check Your Progress

- 1.6 Glossary

- 1.7 Assignment

- 1.8 Activities

- 1.9 Case Study

- 1.10 Further Readings

### 1.0 Learning Objectives:

### After learning this unit, you will be able to understand:

- The Concept of System programming

- Basic of Operating System as a main system program

- Various foundations of systems programming

- Role of assemblers in low level programming

- Idea about working of a loader

- Working of linker in a system.

- Detailed about compiler and interpreter

- Evolution of Operating Systems

### 1.1 Introduction:

During the early days of computing, the on/off switches were used as primitive devices for communication. However, for communicating complex information these traditional devices were not found useful. For this purpose, system programs were developed to make computers better suited to the needs of users. Examples of system programs are operating systems, compilers, interpreters, loaders, linkers, macro processors etc. Further system programs provided assistance to the user to prepare their programs. In this unit, you will study the components of system programming and evolution of operating system.

### 1.2 Components of System Programming:

Operating systems and file systems allow flexible storing and retrieval of information. Compilers are system programs that accept spoken languages, for example, English and translate into machine language. Loaders are system

programs that prepare machine language programs for execution. Macro processors allow programmers to use abbreviations.

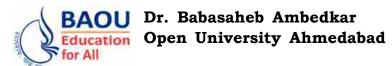

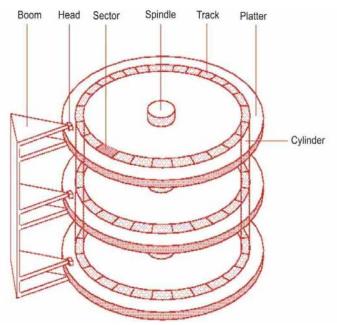

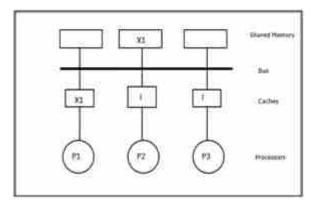

The productivity of computer system is heavily dependent on the effectiveness, efficiency and sophistication of a system program. Fig. 1.1 shows the foundation of system programming.

Fig. 1.1 Foundation of System Programming

As shown in Figure 1.1, the system programming is mainly developed for people who use computer systems. The application program packages are run with system program as a background. For example, an operating system would be required to execute an application program. The system program comprises of operating systems, compilers, interpreters, loaders, linkers, macro processors etc. Utility tools such as text editors, debuggers, search engines etc. are also based on system programs. The management of files, libraries, IO devices also depends largely on system programs.

The major components of a programming system are assembler, macro processor, loader, compilers and operating system :

- 1. Assembler Assembler is the internal program that translates assembly language to machine language. Machine language is in terms of binary numbers that is 0 and the example of assembler is Microsoft Assembler [MASM]. The Input to an assembler is a type of an assembly language program, while output is an object program along with certain information which will allow the loader to arrange the object program for implementation.

- **2. Macro Processor** In macro processor, macro call is contraction for several codes. It is found that a macro definition is a series of code having particular name. So, a macro processor is a program to facilitate and specializes macro description for macro calls.

- **3. Loader** In micro programming, a loader is a routine so as to loads an object program and furthermore get ready for implementation. There are variety of loading schemes such as :

- Absolute

- Relocating

- Direct linking

Generally, a loader should load, relocate as well as link the object program.

**4. Compilers** – A compiler is a program whose purpose is to acknowledge a source program 'in high–level language' in addition to manufactures an equivalent object program. The programming language spoken in

simple English is identified as High Level Language. For example, BASIC is a high level language.

- Introduction to System Programs and System Programming

- **5. Operating System** An operating system is related with the allotment of resources as well as services like:

- Memory

- Processors

- Devices

- Information

An operating system is a significant constituent in a computing system. An operating system is related with distribution of resources as well as services as shown. It corresponds to the program which helps in managing resources like:

- traffic controller

- a scheduler

- memory management module

- I/O programs

- file system

### $\Box$ Check Your Progress – 1:

- 1. Which is not an example of system program?

- a. Operating systems

- c. Compilers

b. MS Office

- d. Interpreters

- 2. \_\_\_\_\_ are system programs that prepare machine language programs for execution.

- a. loaders

- c. Compilers

- b. MS Office

- d. Interpreters

- 3. Which program will translates assembly language to machine language?

- a. Assembler

- c. Compilers

- b. Loader

- d. Interpreters

### 1.3 Evolution of Operating Systems:

The evolution of operating system took place in early sixties. At those time, personal computers with 'on line' operations were not available. It was required to input programs/data through punch cards. The instruction/data would be created by punching holes in cards. Hence these cards are called punch cards. The set of such punched cards would constitute a program. This set would be fed to computer memory. This phenomenon is known as batch processing.

As discussed above, in early computers, there were no operating systems. But when the services of commercial computers started for execution of jobs the scheduling started on batch processing systems. Now, with the advancement of commercial computer services, a number of operating systems software has come into the picture.

Initially, starting with DOS, many operating systems software's were developed such as Unix, Oracle etc. depending on the requirement. The most commonly used operating system is Microsoft Windows. Most of the servers use FreeBSD, Linux and other Unix like systems a lot.

In simple batched system, the memory resource was allocated totally to a single program. Thus, if a program did not need the entire memory, a portion of that resource was wasted. Often in these partitioned memory systems, certain portion could not be used as it was too small to contain a program. The problem of 'holes' or unused portion of core is called fragmentation.

### **❖** Operating System – User Viewpoint : Functions

The purpose of an operating system (monitor) is to assist him in the mechanics of solving problems. Specifically, the following functions are performed by the system :

- Job sequencing, scheduling and traffic controller operation

- Input/output programming

- Protecting itself from the user

- Protecting the user from other users

- Secondary storage management

- Error handling

Secondary storage management is a task performed by an operating system in conjunction with the use of disks, tapes and other secondary storage for a user's programs and data.

An operating system must respond to errors. For example, if the programmer should overflow a register, it is not economical for the computer to simply stop and wait for an operator to intervene. Whenever an error occurs, the operating system must take appropriate action to resolve that.

### **\*** Batch Control Language:

A number of users view an operating system just through the batch system control cards by which they should preface their programs the monitor is a term which refers to the control programs of an operating system. Generally, in a batch system the jobs are stacked in a card reader and the monitor system processes each job in a sequential manner.

A job can consist of numerous separate programs to be executed sequentially, every individual program being called a job step. In a batch monitor system, the user communicates with the system through a control language. In a simple batch monitor system, there are two classes of control cards: execution cards and definition cards.

### Operating system – user viewpoint : Facilities

The function of an operating system is to provide all those facilities, which help to solve problems. This function is applicable for an oriented user the following facilities are conventionally provided by modern operating systems:

- Compilers, such as FORTRAN, COBOL and PL/ I

- Subroutine libraries, such as sine, cosine, square root

- Assemblers

- Linkage editors and program loaders, which bind subroutines together and prepare programs for execution

- Utility routines, such as SORT/MERGE and TAPE COPY

- Application packages, such as circuit analysis or simulation

- Management of system hardware

- Debugging facilities; such as program tracing and 'core dumps'

- Data management and file processing

### **\*** Functions of Operating Systems :

An Operating System contains situation of exceptional programs to facilitate computer system that will require working appropriately. It does various work like

- Identifying input from keyboard

- keeping track of files and directories on disk

- sending output to display screen

- controlling peripheral devices

- OS is considered to provide the following functions:

- Control distribution of resources of computing system between various users as well as tasks.

- Provide interface among computer hardware as well as programmer which shortens in addition to makes possible for coding, creation, debugging of different application programs.

### In addition to above, OS also serves following purposes:

- Convenience It creates a computer suitable to exercise

- **Efficiency** It increases the efficiency of computer system in an efficient manner.

- Ability to evolve It is constructed in such a way that efficient development, testing as well as occurrence of new system functions are permitted.

### **❖** System call:

Modern processors provide processors that can be used as system call. System calls provide interface between a process and operating system. They generate interrupt signal that causes operating system to gain control of the processor.

### **Operating System Services :**

The operating system offers various services to programs and to the users of these programs. Some of the common tasks provided by the operating systems are as follows:

- **Error detection** It is found that error occurs in CPU, I/O device or in memory hardware. It ought to obtain suitable action to make sure for correct as well as reliable computing.

- **File system manipulation** In this, the program will either read or write a file. Here the O/S will allow the program to work on file.

- I/O operation It is related to I/O file or device. The program here will run with the use of any I/O device. This I/O is made available by the operating system.

- **Program execution** The program will get executed inside the memory where the O/S loads the data. Here the program will stop executing normally or unusually.

Introduction to System Programs and System Programming

**Communication** – Data transfer sandwiched between two processes is essential for some time. Together processes behave on single computer or on various computer however, it is associated all the way through computer network. Communication may be put into practice by two methods shared memory as well as message passing.

### $\Box$ Check Your Progress – 2:

- 1. Set of such punched cards will constitute a:

- a. link c. software b. program d. all

- 2. Which is not part of Operating System Services?

- a. Error Handling c. Program Executive

- b. File System Manipulation d. Program deletion

### 1.4 Let Us Sum Up:

The way we write the program to run a computer system is known as system programming. The system program is also called system software.

Examples of system programs are operating systems, compilers, interpreters, loaders, linkers, macro processors etc. Further, system programs provided assistance to the user to prepare their programs.

Operating systems and file systems allow flexible storing and retrieval of information. Compilers are system programs that accept spoken languages, for example, English and translate into machine language. Loaders can be referred to as system programs, which prepare machine language programs for execution. Macro processors allow programmers to use abbreviations.

Thus, the major components of a programming system are assembler, macro processor, loader, compiler and operating system. The evolution of operating system took place in early sixties. At that time, personal computer with 'on line' operations were not available. It was required to input programs/ data through punch cards. The instruction/data would be created by punching holes in cards. Hence, these cards are called punch cards. The set of such punched cards would constitute a program. This set would be fed to computer memory. This phenomenon is known as batch processing. In those days, a FORTRAN programmer would approach the computer with his source deck in his left hand and a green deck of cards that would be a FORTRAN Compiler in his right hand.

From the user's point of view, the purpose of an operating system (monitor) is to assist him in the mechanics of solving problems. Specifically, the following functions are performed by the system:

- Job sequencing, scheduling and traffic controller operation.

- Input/output programming

- Protecting itself from the user; protecting the user from other users

- Secondary storage management

Time-sharing is a method to allocate processor time. It is typically characterized by interactive processing and time-slicing of the CPU's time to allow quick response to each user.

Paging can be referred to as a method of memory allocation through which the program is sub-divided into equal portions or pages and core is sub-divided into equal portions or blocks. The pages are loaded into blocks. Many users view an operating system only through the batch system control cards by which they must preface their programs.

Introduction to System Programs and System Programming

The following facilities are typically provided by modern operating systems :

- Assemblers

- Compilers, are FORTRAN, COBOL and PL/ I

- Subroutine libraries, such as sine, cosine, square root

- Linkage editors and program loaders that bind subroutines together and prepare programs for execution.

- Utility routines, such as SORT/MERGE and TAPE COPY

- Application packages, such as circuit analysis or simulation.

- Debugging facilities; such as program tracing and 'core dumps'

- Data management and file processing

- Management of system

hardware OS is designed to:

- Control allocation of resources of the computing system among various users and tasks

- Allocate a boundary among computer hardware and the programmer for use of coding, creation, debugging programs

### 1.5 Answers for Check Your Progress:

- □ Check Your Progress 1:

- 1. (b), 2. (a) 3. (a)

- □ Check Your Progress 2:

- 1. (b), 2. (d)

### 1.6 Glossary:

- 1. System software It is a system program.

- **2. Loaders** It is a system program which prepares machine language programs for execution.

- **3. Paging** A method of memory allocation by which a program is subdivided into equal portions or pages.

### 1.7 Assignment:

Get information about various System Calls and explain function of any 10 system calls.

### 1.8 Activities:

What are different building blocks in foundation of System Programming? Explain with a diagram.

### 1.9 Case Study:

Discuss with example how the evolution of Operating System took place.

### 1.10 Further Readings:

- 1. Systems Programming, John J. Donovan, Mc-Graw Hill Publishing

- 2. Principles of System Programming, R. M. Graham, Wiley Publishing

- 3. Microprocessor and Assembly Language Programming, D. A. Godse, A. P. Godse Technical Publications

## Unit O2

## ELEMENTS OF ASSEMBLY LANGUAGE PROGRAMMING

### **UNIT STRUCTURE**

- 2.0 Learning Objectives

- 2.1 Introduction

- 2.2 Programming Languages

- 2.3 8085 Assembly Language

- 2.4 Let Us Sum Up

- 2.5 Answers for Check Your Progress

- 2.6 Glossary

- 2.7 Assignment

- 2.8 Activities

- 2.9 Case Study

- 2.10 Further Readings

### 2.0 Learning Objectives:

After learning this unit, you will be able to understand:

- The Concept of Assembly Language Programming

- Features of 8085 assembly language

### 2.1 Introduction:

The computer performs activities as per the instructions given by the user. The set of such instruction written for a particular task is known as computer program. Program is the instruction that tells the computer how to process the data into the form you want. After studying the evolution of operating system concepts, this unit will focus on concepts and features of assembly language programming.

### 2.2 Programming Languages:

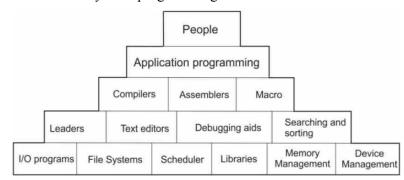

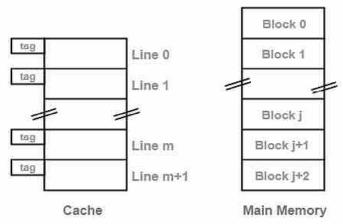

The language in which computer program is written is known as programming language. The programming languages are classified as high level language and Low level language. See Fig. 2.1.

Fig. 2.1 Classification of Programming Languages

Low level language is further classified as assembly language and machine language. Each processor has a fixed set of instructions in form of binary pattern called machine language.

Number of bits that computer can recognise and process at a time is known as a word. The word ranges from 8 bit to 64 bits or even more. One byte comprises of 8 bits. Therefore, the word length ranges from 1 byte to 8 byte.

In machine language, the number of words is fixed for a given processor. For example, 8085 has a fixed word format. Therefore, the number of combinations are 2<sup>8</sup> i.e. 256. The manufacturer develops instructions from these words. One instruction may have one word or more than one word. The manufacturer selects combination of a bit pattern and gives a specific meaning to each combination by using electronic logic circuits. These combinations are called instructions. Set of such instructions is known as assembly language. It is not mandatory for a manufacturer to utilise all 256 word formats for creating instructions.

Machine language is expressed in terms of binary numbers i.e. 0 and 1 as the processor understands binary numbers only. However, for a human being, it is difficult to read and write the program in terms of 0s and 1s.

For example, in order to stop the processing of program execution, the following command is given by 8085 processor in machine language.

01110110

It is really difficult to remember and represent the above instruction expressed in machine language. Therefore, it is expressed in terms of the hexadecimal number as follows:

76 (H)

This code is called hex code or operation code or simply opcode. The opcode for halt i.e. 76 H which is abbreviated by the 8085 manufacturers as HLT. Now it is easy to remember the code HLT for stoppage of the program.

The machine language code is thus simplified by converting it to the code called op code. The op code depends upon type of processor. The program written in op code is known as assembly language code. During the run time, it is necessary to convert op code into machine language so that the processor will understand and process the code. The internal program that translates op code to machine code is known as assembler. The examples of assembler are Microsoft Assembler [MASM], Z–80, 8085, 8086 etc. The assembler for each processor is different.

In assembly language, the binary instructions of machine language are abbreviated. These abbreviated names are known as mnemonics. Thus, assembly language comprises of mnemonics.

Use of assembly language requires knowledge of assembly language and even computer hardware. For everyone it is much convenient to write a program in a High Level Language. The High Level Language comprises of instructions in simple English. Examples of High Level Language are BASIC, FORTRAN and COBOL etc. Compiler is the internal program that translates high level language to machine language. These high level languages are English–like languages such as BASIC, FORTRAN etc.

Elements of Assembly Language Programming

Each processor recognises different sets of instructions in machine language and therefore assembly language. For example, the machine language form 8085, 6800 and Z80 kits are different. Therefore, machine and assembly language is machine dependent. Using high level language, the instructions common to all processors can be written. Therefore, the high level language is machine independent.

A high-level language is a programming language that allows a programmer to develop programs that are not dependent on the type of computer being used. High-level languages are distinguished from machine-level languages by their resemblance to human languages.

When writing a program in a high-level language, the logic of the problem must be given complete attention.

### Advantages of a high-level language

- Because it is written in English-like words, the high-level language is simple to read, write, and maintain.

- The purpose of high-level languages is to overcome the constraint of low-level languages, namely portability. The high-level language is portable, which means that it is machine-independent.

### What is programming?

"Simply put, programming is the act of giving a set of instructions to a computer to execute. If you've ever cooked from a recipe, imagine yourself as the computer and the recipe's author as the programmer. The recipe author gives you a set of instructions to read and then follow. The more complicated the instructions, the more complicated the outcome!"

And programming languages are the means by which we write instructions for computers to follow. Computers "think" in binary, which is made up of strings of 1s and 0s. Programming languages enable us to convert 1s and 0s into something humans can understand and write. A programming language is made up of a series of symbols that act as a bridge between humans and computers, allowing us to translate our thoughts into instructions that computers can understand.

Despite the fact that many languages share similarities, each has its own syntax. After learning the language's rules, syntax, and structure, a programmer writes the source code in a text editor or integrated development environment (IDE). The programmer will then frequently compile the code into machine language that the computer can understand.

### Types of programming languages

Each of the programming languages mentioned in the following section can be classified as one or more of the following types (paradigms).

- High-level (most common) / low-level

- Declarative / imperative / procedural

- General-purpose / domain-specific

- Object-oriented / concurrent

- Command / Compiled / Script language

### List of computer programming languages

### Application and program development

Application and program development is concerned with the development of programs that you use on a daily basis in your workplace. The Internet browser that you are currently using to view the web page, for example, is considered to be a program. If you are interested in creating a program, you might want to consider the following programming languages:

- o C

- o C#

- o C++

- o D

- o Java

- o Swift

- o Tcl

- o Visual Basic

### Artificial intelligence development

AI and related fields include the development of character interactions in computer games, portions of programs that make decisions, chatbots, and other applications of artificial intelligence. If you're interested in creating an artificial intelligence, you might want to consider the following programming languages:

- o AIML

- o C

- o C#

- o C++

- o Prolog

- o Python

### • Database development

Database developers are responsible for the creation and maintenance of databases. When creating or maintaining a database, you should consider using one of the programming languages listed below:

- o DBASE

- o FoxPro

- o MySQL

- o SQL

- o Visual FoxPro

### • Game development

Game development is the process of designing and developing computer games and other forms of entertainment software. If you're thinking about creating a game, you might want to consider one of the following programming languages:

- o C

- o C#

- o C++

- o DarkBASIC

- o Java

### Computer drivers or other hardware development

Computer drivers and programming hardware interface support are required in order for hardware functionality to be achieved. If you're interested in creating drivers or software interfaces for hardware devices, you might want to consider learning one of the following programming languages:

- o Assembly

- o C

### Internet and web page development

The Internet and web page development are at the heart of the Internet's operation. The Internet would not exist if it were not for the efforts of developers. If you're interested in developing web pages, Internet applications, or other Internet-related tasks, you might want to consider learning one of the programming languages listed below:

- o HTML

- o Java

- o JavaScript

- o Perl

- o PHP

- o Python

- o XML

### Script development

It is unlikely that script creation and development will lead to a career, but knowing how to do so can increase productivity for you or your company, resulting in time savings in the thousands of hours. If you're interested in script development, you might want to think about learning one of the following languages:

- o AutoHotkey

- o awk

- o bash

- o Batch file

- o Perl

- o Python

- o Tcl

### □ Check Your Progress – 1:

- 1. The language in which computer \_\_\_\_\_ is written is known as programming language.

- a. Program

- b. Data

- c. Information d. All

- 2. In 8085, the possible word format is:

- a. 256 b. 128

- c. 512

- d. none

### 2.3 8085 Assembly Language:

The assembly language of 8085 comprises 74 instructions having 246 bit pattern. In addition to the instruction set, the 8085 accepts 8 bit data from the input devices and sends it to output devices as per command. The programmer first writes the program in assembly language. He then manually translates the instructions to opcode using table. Then he enters the code the hex keypad of the microprocessor kit. Even though we can write a program using opcode, it is still difficult to understand. It is therefore a good programming practice to write a program using mnemonics. The set of 8085 mnemonics is called 8085 assembly language. In other devices such as Motorola 6800, Zilog Z80 as well as Intel 8085, the assembly language is different. Therefore, the assembly language program written for one microprocessor is not transferable to the other. The machine language and assembly language both are processor specific and non–transferable.

The instruction sets are instruction codes to perform some task. It is classified into five categories.

- Control Instructions (e.g. NOP, HLT, DI, etc.)

- Logical Instructions (e.g. CMP, CPI, ANA, etc.)

- Branching Instructions (e.g. JMP, CC, RET, etc.)

- Arithmetic Instructions (e.g. ADD, ADI, SUB, etc.)

- Data Transfer Instructions (e.g. MOV, MVI, LDA, etc.)

### Addressing Mode in 8085

These are the instructions used to transfer the data from one register to another register, from the memory to the register, and from the register to the memory without any alteration in the content. Addressing modes in 8085 is classified into 5 groups

- Register addressing mode: In this mode, the data is copied from one register to another. For example: MOV K, B: means data in register B is copied to register K.

- **Direct addressing mode:** In this mode, the data is directly copied from the given address to the register. For example: LDB 5000K: means the data at address 5000K is copied to register B.

- Indirect addressing mode: In this mode, the data is transferred from one register to another by using the address pointed by the register. For example: MOV K, B: means data is transferred from the memory address pointed by the register to the register K.

- **Implied addressing mode:** This mode doesn't require any operand; the data is specified by the opcode itself. For example: CMP.

The procedure to write and execute 8085 assembly language using microprocessor kit is given below :

- Write a source code in mnemonics.

- Convert source code to hex code using table.

- Elements of Assembly Language Programming

- Enter (type) the opcode in user memory in sequential order using the hex keypad.

- Execute program by pressing 'execute' key. The answer will be displayed on 7 segments LED.

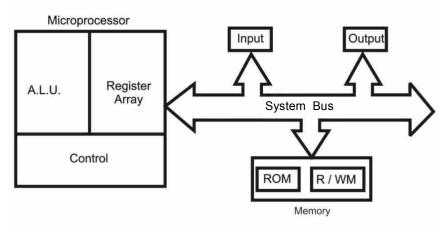

Let us now understand how the microprocessor works. The monitor program of the microprocessor translates hex code to binary code and stores in R/w memory in a sequential manner. When the execute command is given, microprocessor fetches each instruction decodes it and executes it in a sequence till the end of program. Using ASCII keyboard, we can directly enter mnemonics instead of opcode.

Let us write a Machine language program to add two numbers as follows:

00111110 ;Copy value 2H in register A

00000010

00000110 ;Copy value 4H in register B

00000100

10000000 ; A = A + B

It uses English like words to convey the action / meaning called as MNEMONICS. For Example,

MOV to indicate the data transfer

ADD to add two values

SUB to subtract two values

Now, let us write an assembly language program to add two numbers as follows:

MVI A, 2H ;Copy value 2H in register A

MVI B, 4H ;Copy value 4H in register B

ADD B :A = A + B

The above program has the immediate type of instruction called as MVI i.e. Move Immediate and register type of instruction called ADD which will accumulate the value of ACCUMULATOR (Register A) with register B and store the result in register A.

Assembly language is specific to a given processor. For example, assembly language of 8085 is different than that of Motorola 6800 microprocessor.

### $\Box$ Check Your Progress – 2:

- 1. The assembly language of 8085 contains \_\_\_\_\_ instructions with \_\_\_\_\_ bit pattern.

- a. 74, 246

- b. 246, 74

- c. 74, 74

- d. 246, 246

- 2. The 8085 microprocessor have \_\_\_\_\_ addressing mode to store the value inside register.

- a. Immediate

- b. Register

- c. Implicit

- d. None

- 3. Accumulator (Register A) is used to store the answer.

- a. True

b. False

### 2.4 Let Us Sum Up:

The computer performs activity as per instruction given by the user. The set of such instruction written for a particular task is known as computer program. Program is the instruction that tell computer how to process the data into the form you want. Low level language is further classified as Assembly language and machine language. Each processor has a fixed set of instructions in form of binary pattern called machine language. Machine language is expressed in terms of binary numbers i.e. 0 and 1 as the processor understands binary numbers only. However, for a human being, it is difficult to read and write the program in terms of 0s and 1s.

The assembly language of 8085 comprises of 74 instructions having 246 bit pattern. In addition to the instruction set, the 8085 accepts 8 bit data from the input devices and sends it to output devices as per command. The programmer first writes the program in assembly language. He then manually translates the instructions to opcode using table. Then he enters the code the hex key pad of the microprocessor kit. Even though we can write a program using opcode, it is still difficult to understand. It is therefore a good programming practice to write a program using mnemonics. The set of 8085 mnemonics is called 8085 assembly language.

Let us now understand how the microprocessor works. The monitor program of the microprocessor translates hex code to binary code and stores in R/w memory in a sequential manner, When the execute command is given, microprocessor fetches each instruction decodes it and executes it in a sequence till the end of program. Using ASCII keyboard, we can directly enter mnemonics instead of opcode.

### 2.5 Answers for Check Your Progress:

- □ Check Your Progress 1:

- 1. (a), 2. (a)

- □ Check Your Progress 2 :

- 1. (a), 2. (a), 3. (a)

### 2.6 Glossary:

- 1. **Programming language** It is a language in which computer program is written.

- **2. Machine language** It is a set of instructions in form of binary pattern.

### 2.7 Assignment:

Describe the various addressing modes available in 8085 microprocessor.

### 2.8 Activities:

Write an assembly language program to subtract two numbers.

### 2.9 Case Study:

Define the usage of microprocessor in various applications.

2.10 Further Readings:

Elements of Assembly Language Programming

- 1. Systems Programming, John J. Donovan, Mc-Graw Hill Publishing

- Microprocessor and Assembly Language Programming, D. A. Godse,

A. P. Godse Technical Publications

- 3. Principles of System Programming, R. M. Graham, Wiley Publishing

### **ASSEMBLERS**

### **UNIT STRUCTURE**

- 3.0 Learning Objectives

- 3.1 Introduction

- 3.2 Functions of Assembler

- 3.3 Architecture of Assembler

- 3.4 Let Us Sum Up

- 3.5 Answers for Check Your Progress

- 3.6 Glossary

- 3.7 Assignment

- 3.8 Activities

- 3.9 Case Study

- 3.10 Further Readings

### 3.0 Learning Objectives:

After learning this unit, you will be able to understand:

- The Concept of Assembler

- The basic functions of assembler

- The architecture of an assembler

### 3.1 Introduction:

Generally we focus on procedures for producing the machine language. However, the reader must keep in mind that the assembler must also produce other information for the loader to use. For example, externally defined symbols must be noted and passed on to the loader; the assembler does not know the address (value) of these symbols and it is up to the loader to find the programs containing them, load them into core, and place the values of these symbols in the calling program. In this unit we are primarily concerned with the production of machine language.

We have studied that assembler is the program that translates the mnemonics into its machine code. Usually the assembler is not provided on microprocessor kit (single board microcomputer). The program can be entered in mnemonics through ASCII keyboard (Using hex keyboard the program can be types directly in hex code or opcode). Examples of ASCII keyboard are TRS-80 by radio shack and Micro Division by Morrow Design. The assembler translates mnemonics into 8085 machine language code and allocates memory location to each machine code. This avoids manual assembly and errors associated with it. The code can be easily edited. The corresponding changes are made by the assembler in the memory locations and jump sequences.

**Assemblers**

In addition, the assembler calculates constant expressions and solves symbolic names for memory and other entities. The use of symbolic references is an important assembly feature, which saves tedious calculations and manual address updates after changes to the program. Most assembled macro devices also include textual replacement machines - e.g. to generate shorter common sequences of instructions as inline instead of so-called substitutions.

Additionally, some assemblers may be able to perform some simple types of instruction set-specific optimizations, depending on their design. x86 assemblers from various vendors, for example, are widely used and can be considered an example of this. Most of them are capable of performing jump-instruction replacements (long jumps replaced by short or relative jumps) in any number of passes upon request. This process is referred to as "jump-sizing." Another type of assembler is one that simply rearranges or inserts instructions, as is the case with some RISC architecture assemblers, which can assist in optimizing a sensible instruction scheduling in order to exploit the CPU pipeline as efficiently as possible.

Since the 1950s, assemblers have existed as a step above machine language and before high-level programming languages like Fortran, Algol, COBOL, and Lisp. Speedcode is perhaps the best-known example of a class of translators and semi-automatic code generators with properties similar to both assembly and high-level languages.

There may be multiple assemblers with varying syntaxes for a given CPU or instruction set architecture. For example, an instruction to add memory data to a register in an x86-family processor may be written as add eax,[ebx], in the original Intel syntax, but as addl (percent ebx), percent eax in the AT&T syntax used by the GNU Assembler. Despite their differences in appearance, various syntactic forms generate the same numeric machine code. Additionally, a single assembler may have multiple modes to accommodate variations in syntactic forms as well as their precise semantic interpretations (such as FASM-syntax, TASM-syntax, ideal mode, etc., in the special case of x86 assembly programming).

### **Basic Elements of Assembler**

There is considerable variation in how assembler authors categorize statements and in the nomenclature they use. Specifically, some refer to any operation that is not a machine mnemonic or an extended mnemonic as a pseudo-operation (pseudo-op). It is composed of three distinct types of instruction statements used to define program operations:

- Opcode mnemonics

- Data definitions

- Assembly directives

### Opcode mnemonics and extended mnemonics

Instructions (statements) in assembly language, in contrast to high-level languages, are typically very short and straightforward. Mnemonics are symbolic names that are used to identify a single executable machine language instruction (an opcode). There is typically one opcode mnemonic for each machine language instruction that is defined in a computer program. Each instruction is typically composed of an operation code (opcode) and zero or more operands (also known as operands). In most cases, a single value or a pair of values is referred to

in the instruction. Operands can be immediate (a value coded directly into the instruction itself), registers specified explicitly or implicitly in the instruction, or the addresses of data stored elsewhere in storage. This is determined by the underlying processor architecture; the assembler merely reflects the way in which this architecture operates and behaves. In many cases, extended mnemonics are used to specify a combination of an opcode and a specific operand. For example, the System/360 assemblers use B as an extended mnemonic for BC with a mask of 15 and NOP ("NO OPeration" - do nothing for one step) as an extended mnemonic for BC with a mask of 0.

Extended mnemonics are frequently used to support specialized uses of instructions, which are frequently for purposes that are not immediately apparent from the instruction name itself. For example, many CPUs do not have an explicit NOP instruction, but they do have instructions that can be used to accomplish the same result. Nop is implemented in 8086 CPUs using the instruction xchg ax, ax, with nop serving as a pseudo-opcode to encode the instruction xchg ax,ax. Some disassemblers are aware of this and will treat the xchg ax,ax instruction as a nop instruction. For BC and BCR with zero masks, the extended mnemonics NOP and NOPR are used by IBM assemblers for the System/360 and System/370 systems, respectively. These are referred to as synthetic instructions in the context of the SPARC architecture.

Additionally, some assemblers include built-in macros that generate two or more machine instructions. Using some Z80 assemblers, for example, the instruction ld hl,bc is recognised and translated into the values ld l,c followed by ld h,b. These are referred to as pseudo-opcodes in some circles.

Mnemonics are arbitrary symbols; in 1985, the IEEE published Standard 694, requiring all assemblers to use the same set of mnemonics. Since then, the standard has been withdrawn

### **❖** Data directives

Data elements are used to hold data and variables, and instructions are used to define them. The types of data, the length, and the positioning of data are all defined by them. They can also specify whether or not the data is accessible to outside programs (programs that have been assembled separately) or whether it is only accessible by the program in which the data section is defined. Some assemblers group these under the category of pseudo-operations.

### Assembly directives

Assembly directives, also known as pseudo-opcodes, pseudo-operations, or pseudo-ops, are instructions given to an assembler that tell it to "do things other than assemble instructions." Directives affect the assembler's behavior and "may affect the object code, the symbol table, the listing file, and the values of internal assembler parameters," according to the manual. The term pseudo-opcode is sometimes used to refer to directives that generate object code, such as data generation.

To distinguish pseudo-ops from machine instructions, their names frequently begin with a dot. Pseudo-ops can make the program's assembly dependent on parameters entered by the programmer, allowing one program to be assembled in a variety of ways, possibly for different applications. A pseudo-op can also be used to change the way a program is presented to make it easier to read and maintain. Another common application of pseudo-ops is to set aside storage areas for run-time data and, if desired, to set their contents to known values.

**Assemblers**

Programmers can use symbolic assemblers to associate arbitrary names (labels or symbols) with memory locations and constants. Every constant and variable is usually given a name so that instructions can refer to them by name, resulting in self-documenting code. Each subroutine's name is associated with its entry point in executable code, so any calls to it can use that name. GOTO destinations are labelled inside subroutines. Local symbols, which are often lexically distinct from normal symbols, are supported by some assemblers (for example, the use of "10\$" as a GOTO destination).

Some assemblers, such as NASM, offer flexible symbol management, allowing programmers to manage multiple namespaces, calculate offsets within data structures automatically, and assign labels to literal values or the results of simple assembler computations. Labels can also be used to create relocatable addresses for constants and variables.

Like most other computer languages, assembly languages allow comments to be added to program source code that will be ignored during assembly. Assembly language programs require careful commenting because the meaning and purpose of a sequence of binary machine instructions can be difficult to decipher. When changes must be made, the "raw" (uncommented) assembly language generated by compilers or disassemblers is difficult to read.

### 3.2 Functions of Assembler:

The fundamental functions of an assembler are to translate mnemonic operation codes to their machine language equivalents, and then it assigns machine addresses to symbolic labels by the programmer.

The basic assembler functions are as follows:

- Translating mnemonic language to its equivalent object code.

- Assigning machine addresses to symbolic labels.

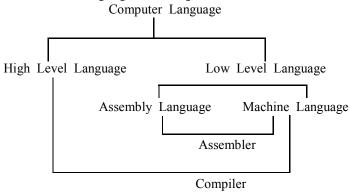

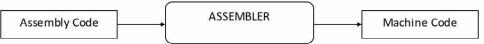

Fig. 3.1 Function of an Assembler

Let us understand the working of assembler with some example.

The on/off switches are connected to the input port having address 00H and turn on devices are connected to the output port with address 01H. The suffix H indicates that the addresses are given in hexadecimal numbers.

The input has eight switches connected to the data bus through a tristate buffer. Any one of the switches can be connected to 5 V (logic 1) or ground (logic and each switch controls the corresponding devices at output port. The microprocessor is required to read the bit pattern on the switches and send the same bit pattern to the output port in order to turn on the corresponding devices :

Instructions IN 00H

OUT 01H

HLT

When the microprocessor executes instruction H, it enables the tri-state buffer. The bit pattern formed by the switch position is placed on data bus and transferred to the accumulator. This is called reading of the input port.

When the microprocessor executes next instruction OUT 01H, it places the controls of the accumulator on the data bus and enables output port 01H. This is also called writing data to an output port. The output port latches the bit pattern and turns on/off the devices connected to the output port according to the bit pattern.

The drawback of the above program is the program reads switch positions once and stops. Therefore, if you want to turn on/off different devices, you have to reset the system and start it over again. This is impractical in real life situations. However, the unconditional jump condition (JNP), in place of HLT instruction will allow the microprocessor to monitor switch positions continuously.

The above program can be modified to read the switch positions continuously and turn on the appliances accordingly as follows:

START: IN 00H

OUT 01H

JMP START

The machine code and comments can be included in the above program as follows:

| Memory<br>Address | Machine<br>Code | Label | Mnemonics | Comments                                              |

|-------------------|-----------------|-------|-----------|-------------------------------------------------------|

| 2000<br>2001      | DB<br>00        | START | IN 00H    | Read input switches                                   |

| 2002<br>2003      | D3<br>01        |       | OUT 01H   | Turn on the devices according to the switch positions |

| 2004              | C3              |       | JMP START | Go back to beginning and read the switches again      |

The above program includes more than one column called label. Memory location of 2000H is defined with a label START. Therefore the operand of jump instruction is specified with label START. The program sets up an endless loop and the microprocessor monitors the input port continuously, the output will reflect any change in the switch position.

The above program is written considering manual assembly. That is, first we write mnemonics and then we translate corresponding hex code (machine code) as shown in the above example. This hexcode is entered through the hex keypad provided on microprocessor kit.

Now using ASCII keyboard, we can enter mnemonics directly using assembler. The assembler will convert mnemonics to machine code. The assembler program includes following assembler directives.

**Assemblers**

| Label | Mnemonics | Comments                                |  |

|-------|-----------|-----------------------------------------|--|

| PORT0 | EOQ 00H   | Input Port Address                      |  |

| PORT1 | OUT 01H   | Output Port Address                     |  |

|       | ORG 2000H | Start assembling the program from 2000H |  |

| START | IN PORT0  | Read input switches                     |  |

|       | OUT PORT1 | Turn on devices                         |  |

|       | JMP START | Go back and read switches               |  |

| END   |           |                                         |  |

The commands given through assembler are called assembler directives. The above program illustrates following assembler directives.

- **ORG** The object code will be stored starting at location 2000 H.

- EQU The directive EQU is the abbreviation of the word 'equate'. The program defines two equates: PORT0 and PORT1. In this program it would be easier to write port addresses directly with the instructions. The equates are essential in development projects in which hardware and software design are done concurrently. In such a situation, equates are convenient. Equates are also useful in long programs because it is easy to change or define port addresses by defining equates.

- Label The program illustrates one label START.

- END End of assembly.

### $\Box$ Check Your Progress – 1:

| 1. | The system program that accepts assembly language program as input and produces its machine language equivalent know as |                             |  |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|

|    | a. Assembler b. Loader                                                                                                  | c. Compiler d. Interpreter  |  |  |  |

| 2. | JMP mnemonic can be used for                                                                                            |                             |  |  |  |

|    | a. Jump on specified label                                                                                              | b. Describe the information |  |  |  |

|    | c. Retrieve information                                                                                                 | d. None                     |  |  |  |

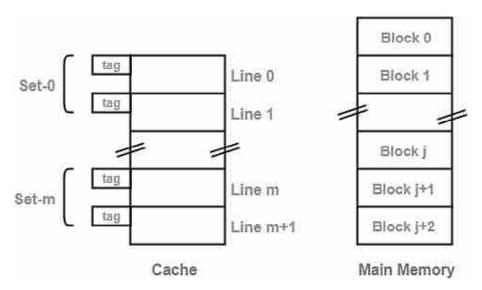

### 3.3 Architecture of Assembler:

### **Single Pass Assembler:**

The assemblers that complete the whole assembly process within one pass, i.e. one reading of the program are called single pass assemblers. The assembler scans the source program instruction by instruction and translates them in machine codes. If there is instruction which is defined later in the program, but referenced earlier (i.e. forward reference problem) then the assembler leaves the address of that particular symbol or operand and process further. This forward reference symbol is entered in the symbol table and marked as undefined. Another list of instructions which use this symbol is also maintained. When the symbol definition is encountered, the assembler inserts the address in the symbol table. It also inserts the address to the instructions which use this symbol in the list of forward references. The object code in single pass assemblers can be produced in two ways. First, compile and loading scheme, in which the object code is directly loaded into the main memory for execution. So, no separate loaders are required. Secondly, the object program is stored

secondary memory and loaded later in main memory for execution. Thus, separate loader is used.

It generates instructions by evaluating the mnemonics (symbols) in operation field and finds the value of symbol and literals to produce machine code. Now, if assembler do all this work in one scan then it is called single pass assembler, otherwise if it does in multiple scans then called multiple pass assembler.

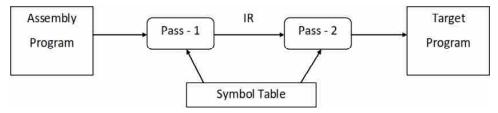

### **\*** Two Pass Assembler:

To arrange the program, the assembler examines throughout the program twice whose process is termed as two pass assembler.

### • Pass 1:

- 1. Define symbols and literals and remember them in symbol table and literal table respectively.

- 2. Keep track of location counter.

- 3. Process pseudo-operations.

### • Pass 2:

- 1. Generate object code by converting symbolic op-code into respective numeric op-code.

- 2. Generate data for literals and look for values of symbols.

During initial period, the first memory place is calculated from ORG statement furthermore makes the location counter to initialize. Further, the assembler will go through every instructions as well as records in address column of initial byte of instruction. The vision of location counter is to look all the way to every byte in the program. The assembler in addition, will produce a symbol table for the initial period. When it comes across a label, it records a label and its location.

During the next stage, every instruction is observe furthermore the mnemonics as well as labels are changed by machine hex notation which can be visualized as :

### **♦** Pass 1 :

| Address<br>Hex | Machine<br>Code Hex | Label Opcode | Operand | Symbol Table |

|----------------|---------------------|--------------|---------|--------------|

| 2000           |                     | START : IN   | PORT0   | PORTO 00H    |

| 2002           |                     | OUT          | PORT1   | PORT1 01H    |

| 2004           |                     | JUMP         | START   | START 2000H  |

**Assemblers** \* Pass 2:

| 2000 | DB00   |  |

|------|--------|--|

| 2002 | D301   |  |

| 2004 | C30020 |  |

### **Assembled Print File:**

The assembled print file lists the memory address of the first byte of each instruction.

This program monitors the switch positions of the input port and turn on/off devices connected to the output port.

0000 = PORTO EQU 00H; Input port address

0001 = PORT1 EQU 01H; Output port address

2000 ORG 2000H; Start assembling program from location

: 2000H

2000 DB00 IN PORT0; Read input switches

2002 D301 OUT PORT1; Turn on devices

2004 C30020 JMP START; Go back and read switches again

2007 END

The example of assembled print file is shown above. The comments are started with; mark. The equate relationship is indicated by = mark.

#### **Check Your Progress - 2:**

1. In the program

START: IN 00H

OUT 01H

JMP START

IN 00H denotes

- a. Read input switches

- b. Read output switches

- c. Turn on the devices

- d. Turn off the devices

- 2. All the machine opcode is stored inside

- a. MOT Table b. Base Table

- c. POT Table d. LC

- The forward reference is a main problem in One Pass Assembler. 3.

- a. True b False

### 3.4 Let Us Sum Up:

Assembler is the program that translates the mnemonics into its machine code. Usually the assembler is not provided on microprocessor kit (single board microcomputer). The program can be entered in mnemonics through ASCII keyboard (Using hex keyboard the program can be types directly in hex code or opcode). Examples of ASCII keyboard are TRS-80 by radio shack and Micro Division by Morrow Design. The assembler translates mnemonics into 8085 Machine language code and allocates memory location to each machine code. This avoids manual assembly and errors associated with it. The code can be easily edited. The corresponding changes are made by the assembler in the

memory locations and jump sequences. In order to assemble the program, the assembler scans through program twice, this is known as a two pass assembler.

#### 3.5 Answers for Check Your Progress:

#### □ Check Your Progress 1:

1. (a), 2. (a)

# □ Check Your Progress 2:

1. (a), 2. (a) 3. (a)

# 3.6 Glossary:

- 1. **Assembler** It is system program that translate mnemonic operation codes to their machine language equivalents.

- 2. **Single Pass Assembler** Forward reference is the problem in this type of assembler

- **Two Pass Assembler** Pass 1 define the symbols (assign addresses) and Pass 2 assemble instructions and generate object program.

#### 3.7 Assignment:

Describe the one pass assembler with its limitation in your words.

#### 3.8 Activities:

Discuss how the two pass assembler is used in 8085 microprocessor.

### 3.9 Case Study:

Elaborate the Machine – Dependent Assembler features and Machine – Independent Assembler features.

### 3.10 Further Reading:

- 1. Systems Programming, John J. Donovan, Mc-Graw Hill Publishing

- Microprocessor and Assembly Language Programming, D. A. Godse,

A. P. Godse Technical Publications

- 3. Principles of System Programming, R. M. Graham, Wiley Publishing

# Unit

04

# THE MACRO PROCESSOR AND LOADERS

# **UNIT STRUCTURE**

- 4.0 Learning Objectives

- 4.1 Introduction

- 4.2 Macro Instructions

- 4.3 Macro Processor

- 4.4 Loaders

- 4.5 Let Us Sum Up

- 4.6 Answers for Check Your Progress

- 4.7 Glossary

- 4.8 Assignment

- 4.9 Activities

- 4.10 Case Study

- 4.11 Further Readings

# 4.0 Learning Objectives:

#### After learning this unit, you will be able to understand:

- The Macro Instructions and concepts of Macro Processor

- Role of loaders

- Working of compile and go loaders

- Functions of general loader scheme

- Application of absolute loaders

- Concept of Direct linking loader

# 4.1 Introduction:

A macro processor is a program that copies a stream of text from one place to another, making a systematic set of replacements as it does so. Macro processors are often embedded in other programs, such as assemblers and compilers. Sometimes they are standalone programs that can be used to process any kind of text.

Macro processors have been used for language expansion (defining new language constructs that can be expressed in terms of existing language components), for systematic text replacements that require decision making, and for text reformatting

#### 4.2 Macro Instructions:

A Macro instruction is the notational convenience for the programmer. For every occurrence of macro the whole macro body or macro block of statements gets expanded in the main source code. Thus Macro instructions make writing code more convenient.

A macro instruction is a group of programming instructions that have been compressed into a simpler form and appear as a single instruction. When used, a macro expands from its compressed form into its actual instruction details. Both the name of the macro definition and other variable parameter attributes are included within the macro statement.

Macro instructions were first used in the assembler language rather than a higher-level programming language. The way a macro expands to a set of instructions depends on the macro definition, which converts the macro into its detailed instructional form.

Macros save developers much time and effort, especially when dealing with a certain sequence of commands that is repeated more than once within the program body. Macros also save space and spare the programmer time spent on a long code block that may pertain to performing a single function.

The concept of macros is used within some precompilers, while higher–level languages focus on simplifying program and function writing, which makes the macro instruction a common element among most high–level programming languages. Macro instructions are generated together with the rest of the program by the assembler.

For example, before calling a subroutine, the contents of all registers may need to be stored. This routine work can be done using a macro. This requires a sequence of instructions. We can define and use a macro, SAVEREGS, to represent this sequence of instructions.

#### 4.3 Macro Processor:

In order to relieve a programmer from the need to repeat identical parts of his program, operating systems provide macro processing facilities, which allow programmers to define abbreviations for a part of his program and to use these abbreviations in his program so as to avoid repeated use of identical code. The macro processor treats abbreviation as a macro definition. The macro processor substitutes definitions for all occurrences of abbreviation in the program such abbreviations are called macro calls.

In addition to this task, the macro processors are also used as general text handlers and for specializing operating systems to individual computer installations. To specialise an operating system, series of macro calls are written. These are processed by the macro processor by substituting appropriate definitions, thereby producing all the programs for an operating system. As we have seen above, macro is the simplest form of abbreviation for a sequence of operations. Consider the following program.

```

A 1, DATA "Add contents of DATA to register 1"

```

A 2, DATA "Add contents of DATA to register 2"

A 3, DATA "Add contents of DATA to register 3"

.

.

A 1, DATA "Add contents of DATA to register 1"

A 2, DATA "Add contents of DATA to register 2"

A 3, DATA "Add contents of DATA to register 3"

DATA DC, F5

The Macro Processor and Loaders

In the above program, the following sequence occurs twice:

A 1, DATA

A 2, DATA

A 3, DATA

Using macro allows us to assign name to a sequence and to use that name in it's a macro facility permits us to assign name to this sequence and to use this name in its place. We can invent a macro language that allows us to specify the above as macro definition and allows us to refer the definition later. The macro processor effectively constitutes a separate language processor with its own language.

The name is attached to a sequence by means of macro instruction definition. This definition is formed in the following manner :

MACRO ===> Start of definition

INCR ===> Macro Name

A 1, DATA

A 2, DATA

A 3, DATA

MEND ===> End of definition

The MACRO pseudo-op is the first line of definition and identifies the following line as a micro instruction name. Following the name line is a sequence of instructions being abbreviated the instructions comprising the macro instruction. This definition is terminated by a line with MEND (macro end) pseudo op.

Once the macro has been defined, the use of macro name as an operation mnemonic in an assembly system is equivalent to the use of corresponding instruction sequence. The above example is re-written as follows, assigning the name INCR to the repeated sequence.

In this case the macro processor replaces the macro call with the lines:

A 1, DATA

A 2, DATA

A 3, DATA

| Source                                | Expanded source                  |

|---------------------------------------|----------------------------------|

| MACRO INCR A 1,DATA A 2,DATA A 3,DATA | A 1,DATA<br>A 2,DATA<br>A 3,DATA |

| MEND                                  |                                  |

| INCR                                  | A 1,DATA                         |

|                                       | A 1,DATA<br>A 2,DATA<br>A 3,DATA |

|                                       |                                  |

|                                       |                                  |

| INCR                                  | DATA DC F5                       |

|                                       |                                  |

The process of replacement is called expanding the macro. The macro definition does not appear in the expanded source code. This definition is saved by the macro processor. As the macro name occurs in the source program it has to be expanded and the process is called a macro call.

#### $\Box$ Check Your Progress – 1:

- 1. If the instructions are repeating in the program, then \_\_\_\_\_is used to lower the length of such program.

- a. procedure

b. subroutine

c. macro

- d. none of the above

- 2. In programming, the macro present inside the macro is known as

- a. macro in macro

- b. nested macro

- c. macro inside macro

- d. none of the above

- 3. Which of the following language provide built in facilities for writing macros

- a. C

- b. C++

- c. Ada

- d. All of the above

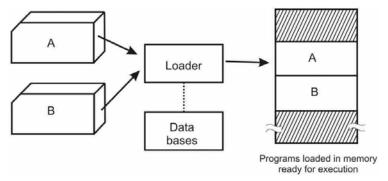

#### 4.4 Loaders:

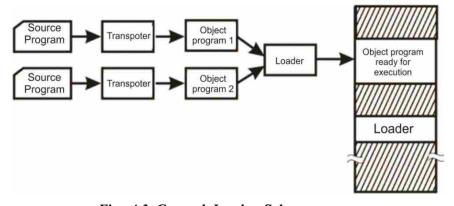

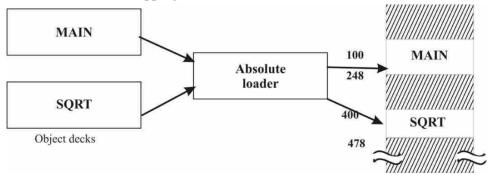

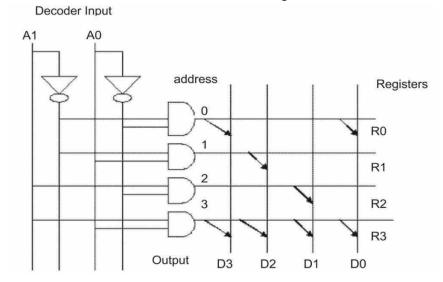

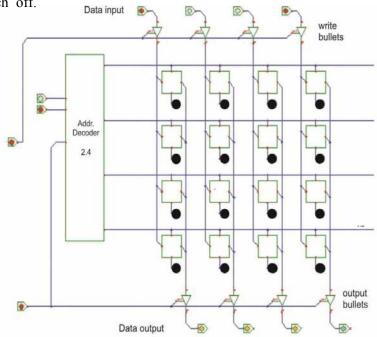

We have studied that the user programs which normally gets converted to object programs (machine language) by assemblers, compilers or interpreters. Loader is a program, which accepts object programs, prepares them for execution by the processor and initiates the execution. This is shown in the general loading scheme (Fig. 4.1).

Fig. 4.1 General Loading Scheme

Basically, the loader performs following four functions:

- Allocate space in memory for the program (allocation).

- Resolve symbolic references between object desks (linking).

- Adjust all address dependent locations such as address constants to respond to the allocated space (relocation).

- Physically place the machine instructions and data into the memory (loading).

**Loader Schemes :** The loader schemes provide various ways of loading. The main loader schemes are discussed below :

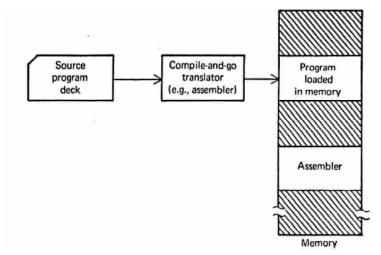

#### 1. Compile and Go Loader:

In this scheme, the assembler runs in this part of memory. The assembled machine instructions and data are placed directly in the assigned memory locations. When the assembly gets completed, the assembler causes a transfer

The Macro Processor and Loaders

to staring instruction of the program. This is the simple solution involving no extra procedures. Such a loading scheme is commonly called "compile-and-go" or "assemble-and-go". See the Fig. 4.2.

Fig. 4.2 "Compile and go" loader scheme

The assembler just places code into core and the loader comprises one instruction which transfers to the starting instruction of the newly assembled program. Apart from this, there are certain disadvantages of using this method. First, portion of the memory is wasted because the core occupied by the assembler is unavailable to the object program. Second, it is required to retranslate (assemble) the user's program every time during its run. Third, it is very difficult to handle multiple segments, especially if the source programs are in different languages.

#### 2. General Loader Scheme:

Fig. 4.3 General Loader Scheme

The outputting of instructions and data as they are assembled circumvents the problem of wasting core for the assembler. That type of an output could be saved and loaded whenever the code has to be executed. The assembled programs could be loaded into the same area in core that the assembler occupied (since the translation will have been completed). This type of output form, which may be on cards containing a coded form of instructions, is called an object deck.

The use of object deck as intermediate data to avoid one disadvantage of preceding 'compile-and-go' scheme requires addition of new program to the system, a loader.

The function of the loader is to allow the machine instructions, data and useful information in shape of object layout and keeps the instructions and

data in the centre of an executable structure. It is found that more memory can be stored in the loader as it is smaller as compared to assembler.

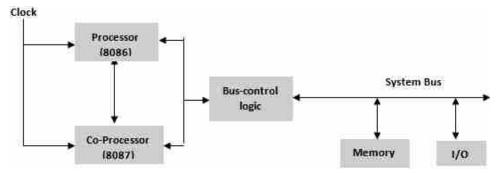

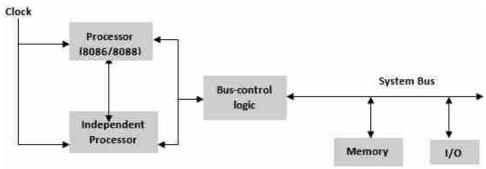

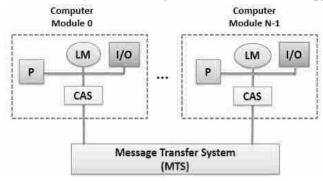

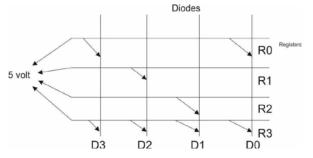

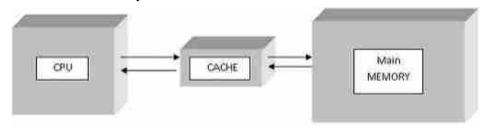

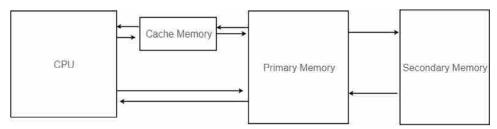

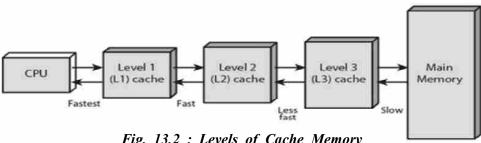

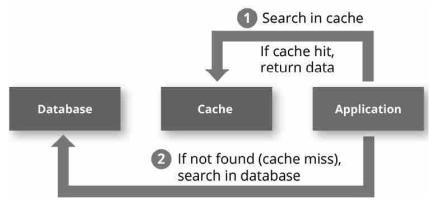

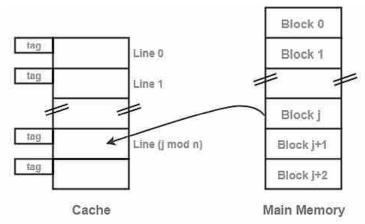

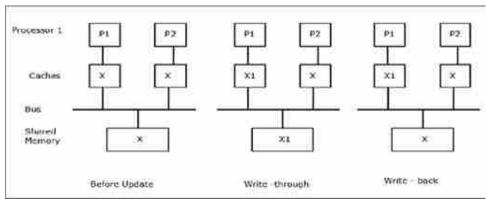

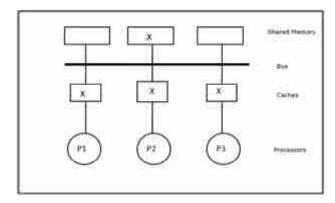

So the assemblers and compilers being the program converter that will form an equivalent object program and with the help of linkage conventions will write subroutines in many different languages for further action by the loader in machine language.